Company Overview

Aldec, Inc. is an industry-leading Electronic Design Automation (EDA) company delivering innovative design creation, simulation and verification solutions to assist in the development of complex FPGA, ASIC, SoC and embedded system designs. View Product Line (pdf)

With an active user community of over 35,000, 50+ global partners, offices worldwide and a global sales distribution network in over 43 countries, the company has established itself as a proven leader within the verification design community.

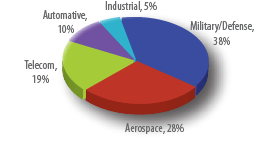

Market

Aldec market share is estimated at 38% of all mixed-language RTL Simulators sold to FPGA designers worldwide. (Excludes OEM simulators supplied directly from FPGA vendors).

Aldec delivers high quality EDA solutions for government, military, aerospace, telecommunications, automotive and safety critical applications. Large companies including IBM, GE, Qualcomm, Texas Instruments, Applied Micro, Hewlett Packard, Toshiba, Intel, NEC, Mitsubishi, LG, Hitachi, NASA, Invensys, Westinghouse, Raytheon, Panasonic, Lockheed Martin, Samsung, as well as mid-size and small firms utilize Aldec EDA verification suites to boost product performance, cut design development cycles and reduce cost.

Technology Patents

- US Patent#4,791,357: Electronic circuit board testing system and method

- US Patent#4,827,427: Instantaneous incremental compiler for producing logic circuit

- US Patent#5,479,355: System and method for closed loop operation of schematic designs with electrical hardware

- US Patent#5,051,938: Simulation of selected logic circuit designs

- US Patent#6,578,133: MIMD Array of Single Bit Processors for Processing Logic Equations in Strict Sequential Order

- US Patent#6,915,410: Compiler synchronized multi-processor programmable logic device with direct transfer of computation results among processor

- US Patent#7,003,746: Method and apparatus for accelerating the verification of application specific integrated circuit designs

Milestones |

|

| 2021 | |

|

|

| 2020 | |

|

|

| 2019 | |

|

|

| 2018 | |

|

|

| 2017 | |

|

|

| 2016 | |

|

|

| 2015 | |

|

|

| 2014 | |

|

|

| 2013 | |

|

|

| 2012 | |

|

|

| 2011 | |

|

|

| 2010 | |

|

|

| 2009 | |

|

|

| 2008 | |

|

|

| 2007 | |

|

|

| 2006 | |

|

|

| 2005 | |

|

|

| 2004 | |

|

|

| 2003 | |

|

|

| 2002 | |

|

|

| 2000 | |

|

|

| 1999 | |

|

|

| 1997 | |

|

|

| 1996 | |

|

|

| 1992 | |

|

|

| 1985 | |

|

|

| 1984 | |

|

|

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.