HES7BPX4 Backplane Board

HES7BPX4 is a backplane board used to build scalable hardware platforms for emulation and prototyping based on HES-US or HES-7 FPGA main boards. The largest configuration can supply up to 633 Million ASIC gates. The backplane is build of non-proprietary BPX connectors matching ones used on HES main boards to provide passive cross board I/O interconnections. Careful design of clock distribution tree assures flexibility and configurability from a host PC. There is a special backplane controller implemented in Spartan-6 FPGAs, that integrates JTAG chains and debug buses from all main boards and provides a common programming port to all FPGA logic modules in the system.

Configurations

|

Main Board |

FPGA Technology |

# FPGA |

ASIC Gates |

|

4x HES-US-2640 |

Virtex UltraScale XCVU440 |

24 |

633 Million |

|

4x HES-US-1320 |

Virtex UltraScale XCVU440 |

12 |

316 Million |

|

Virtex-7 2000T |

24 |

288 Million |

|

|

4x HES7XV4000BP |

Virtex-7 2000T |

8 |

96 Million |

HES7BPX4 Backplane Board

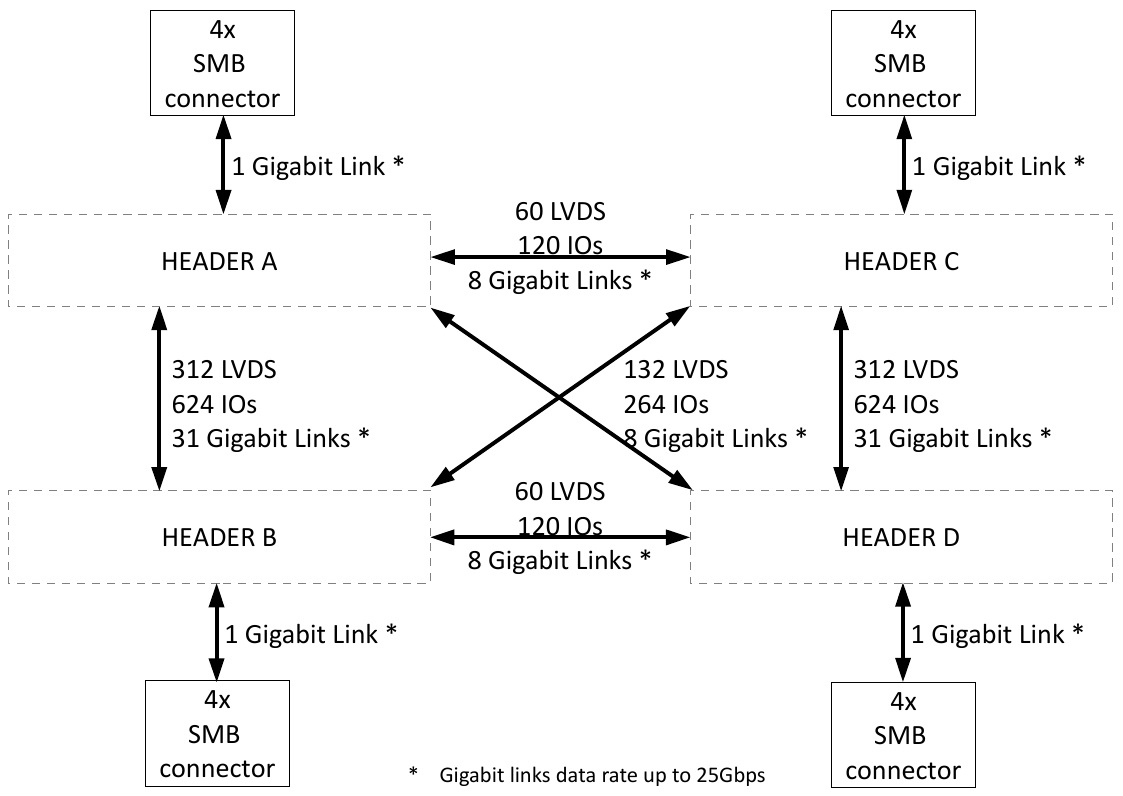

Connectivity

- Symmetrical interconnections between boards in headers A-D

- High speed (25 Gbps) connectors: MOLEX 76150 series

- 2016 I/O (1008 DIFF) - standard GPIO optimized for LVDS & TDM

- 94 GTX/GTH - high speed serial I/O

Clocking

- Reconfigurable clock network based on crosspoint switches

- Dynamic routing of 4 clock lines from any to any main board

- LVDS clocks, high level of signals integrity and immunity to distractions

- Crosspoint switch: DS10CP154ATSQ

- 4 dedicated clocks for GTX/GTH

- 3 oscillators: 100 MHz, 125 MHz, 250 MHz

- 1 external SMB connector

- routed through crosspoint switch and fanout buffers

- Global reference clock routed to programming controllers on all main boards and backplane

Configuration & Hosting

- 2 Spartan-6 FPGA used for board control, diagnostics and clocks configuration

- Centralized FPGA programming in backplane configurations

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.