FPGA Design Creation and FPGA Simulation

Active-HDL™ is a Windows® based, integrated FPGA design creation and simulation solution for team-based environments. Active-HDL’s integrated design environment (IDE) includes a full HDL and graphical design tool suite and RTL/gate-level mixed-language simulator for rapid deployment and verification of FPGA designs.

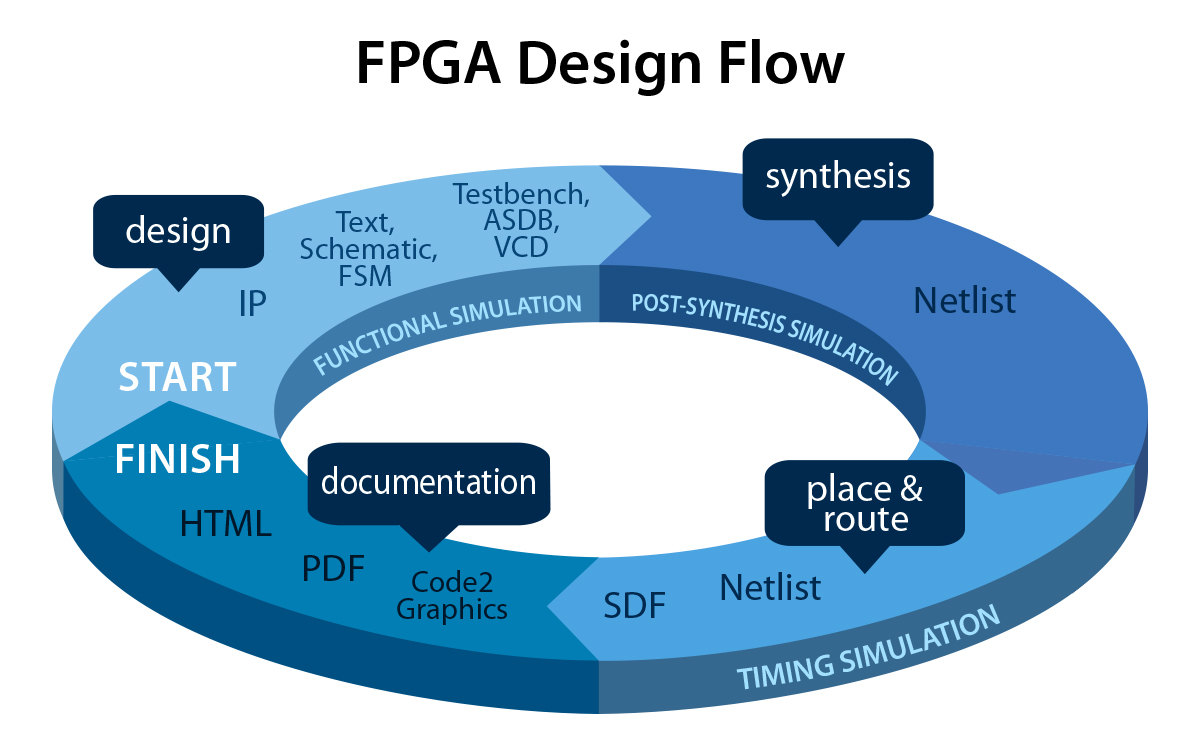

The design flow manager evokes 200+ EDA and FPGA tools, during design entry, simulation, synthesis and implementation flows and allows teams to remain within one common platform during the entire FPGA development process. Active-HDL supports industry leading FPGA devices from AMD, Intel, Lattice, Microchip, Quicklogic and more.

Top Features and Benefits

-

Unified Team-based Design Management maintains uniformity across local or remote teams

-

Configurable FPGA/EDA Flow Manager interfaces with 200+ vendors tools allows teams to remain on one platform throughout FPGA development

-

Quickly deploy designs by using Text, Schematic and State Machine

-

Distribute or deliver IPs using more secure and reliable Interoperable Encryption standard

-

Powerful common kernel mixed language simulator that supports VHDL, Verilog, SystemVerilog and SystemC

-

Ensure code quality and reliability using graphically interactive debugging and code quality tools

-

Perform metrics driven verification to identify unexercised parts of your design using Code Coverage analysis tools

-

Improve verification quality and find more bugs using ABV - Assertion-Based Verification (SVA, PSL)

- Ability to simulate advanced verification constructs like SV Functional Coverage, Constrained Randomization and UVM

-

Connect the gap between HDL simulation and high level mathematical modeling environment for DSP blocks using MATLAB®/Simulink® interface

-

Abstract design intelligence and represent them in easy to understand graphical form using HDL to schematic converter

-

Share designs quickly with auto-generate Design Documentation in HTML and PDF

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.