FPGA Test System

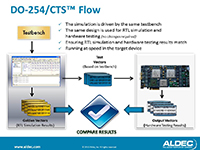

DO-254/CTS™ is a fully customized hardware and software platform that augments target board testing to increase verification coverage by test and satisfy the verification objectives of DO-254/ED-80. The target design runs at-speed in the target device mounted on the custom daughter board. The simulation testbench is used as test vectors to enable requirements-based testing with 100% FPGA pin-level controllability and visibility necessary to implement normal range and abnormal range tests. The FPGA testing results are captured at-speed and displayed using a simulator waveform viewer for advanced analysis and documentation.

Top Features

|

Aldec, Inc.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.

Printed version of site: support.aldec.com/en/products/mil_aero_verification/do-254