SoC Co-emulation

Co-emulation means connecting an emulated design with surroundings that make up the operating conditions for the emulated design. It can be used within different environments and for different purposes.

- Connecting with Virtual Platforms – for complete system verification

- Connecting with Virtual Peripherals – for modeling operating environment

- In Circuit Emulation – for testing within real operating environment

- Connecting with software debuggers – for firmware development and validation

Environments and purposes can be mixed with each other.

Virtual Platforms

In the SoC era, Virtual Platforms (VP) became commonly used for system architecture exploration and, following this, as a golden reference model for SoC verification. It turns out that VPs are also very useful when it comes to firmware and software development as the virtual reference models are usually available much earlier than the SoC prototype.

Co-emulation with VP offers numerous advantages to design, development and verification teams.

Advantages of co-emulation with Virtual Platforms:

- Emulator replaces lacking virtual models (e.g. custom peripherals)

- VP replaces modules unavailable in RTL code (e.g. licensed processors like ARM® Cortex)

- Emulation ensures real hardware accuracy

- Emulator is faster than complex virtual model

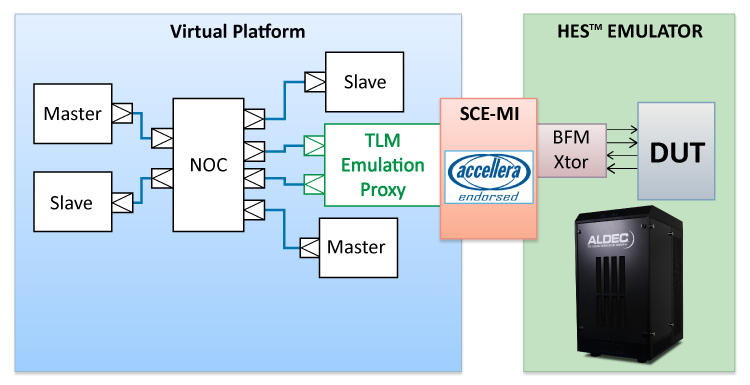

Virtual Platforms are usually based on SystemC simulation kernel and use TLM as an interface to interconnect simulated models. The same interface is used to connect with emulated design.

HES-DVM provides speed optimized implementation of Accellera’s SCE-MI infrastructure which is used as a channel to transfer messages between virtual platform and emulator. The SCE-MI C/C++ API can be easily wrapped within TLM Proxy modules and seamlessly integrated in any kind of SystemC/TLM Virtual Platform. The SCE-MI is appropriate to implement various timing accuracy including untimed or loosely timed models. Aldec’s HES™ has been used successfully with several third party virtual platforms like ARM® Fast Models, Imperas OVP or ones from other EDA vendors.

Availability of proven Verification IPs is equally important to successful design verification. Connecting emulator with virtual platform requires Bus Functional Model transactors (BFM Xtor) of a given bus interface and TLM Emulation Proxy module to be instantiated within the Virtual Platform. Currently Aldec provides transactors with TLM 2.0 proxy wrappers for AMBA AHB, AXI and OCP buses.

Benefits:

- Hybrid environment VP+EMU makes possible verification of complete SoC without need to compromise speed and accuracy

- Seamless integration of fast FPGA based emulation with Virtual Platforms

- Accellera’s SCE-MI enables reuse and increases productivity

- Support for standard SystemC/TLM interfaces and different timing accuracy

- Out of the box support for AMBA AHB, AXI and OCP interfaces

- Emulated modules have RTL accuracy but run fast enough for VP

- Automated emulation setup

Virtual Peripherals

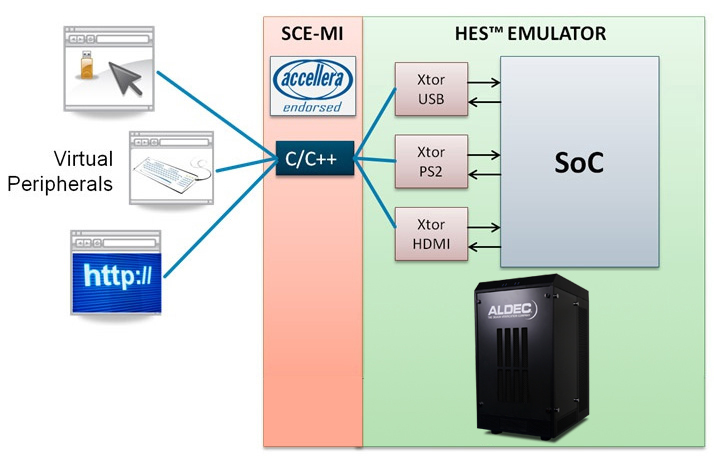

Even though Systems on Chip (SoC) integrate increasingly more functions on a single die, they will always require connecting external peripherals like displays, keyboards, sensors, multimedia ports, etc. Therefore a complete SoC verification environment should have proper models of all peripherals. One way is to use virtual peripherals, which are applications running on an emulation host or even remotely and connect to emulated design using transactors.

Aldec’s HES-DVM provides speed optimized implementation of Accellera’s SCE-MI standard that is an ideal framework for developing reusable transactors and virtual models.

Aldec also provides a number of ready to use transactors for interfaces like: USB, Gigabit Ethernet, HDMI, VGA, PCIe, JTAG, UART, I2C and others. They have simple to use API for quick development and integration of virtual peripherals. For more information check in Verification IP page.

Benefits:

- Reusable virtual peripherals implementation based on SCE-MI

- Complete SoC verification environment including user interfaces

- Easy maintenance and re-configuration of verification environment

- Instantly available transactors of most commonly used interfaces

- Alternative to demanding In Circuit Emulation

In Circuit Emulation

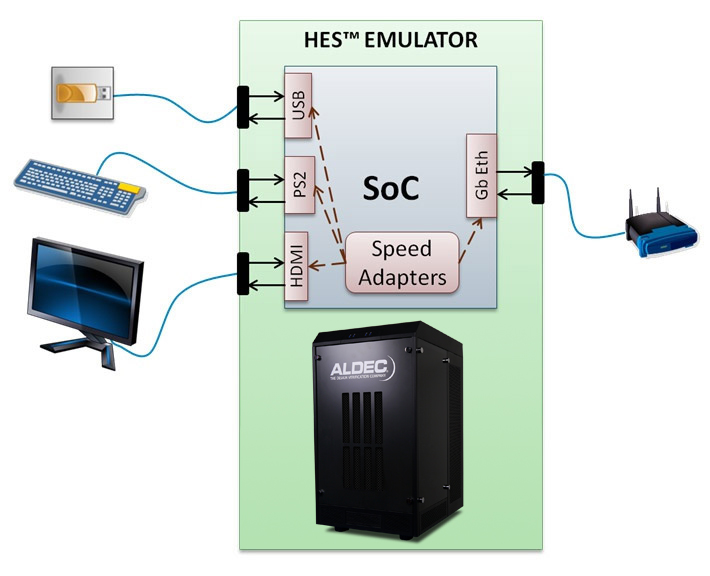

The ICE is a traditional approach to verification of emulated design with external peripherals for which real devices are connected to the emulator.

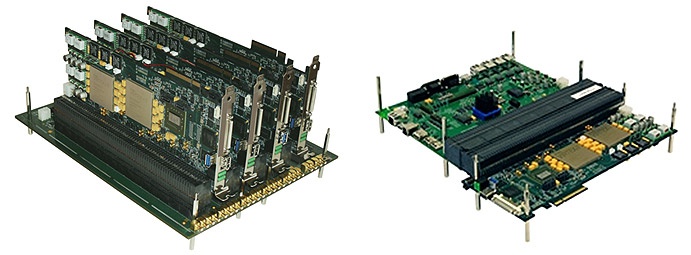

Emulators based on FPGA prototyping boards have a significant advantage over dedicated emulation boxes which is larger number of different connectors. Moreover these connectors are tied up to different FPGAs on multi-FPGA boards facilitating external devices connection and design partitioning. It is much easier to develop specialized daughter boards with PHY devices and connect them to FPGA prototyping boards if they use non proprietary connectors. This is the case of HES-7 and usually of in-house developed boards.

In the ICE it is often required that external device runs at its target speed which is higher than speed of emulated clocks. This is the case where speed adapter modules are used. They can be treated as a special kind of Verification IP that separates real clock domain from emulated clock and additionally buffers data transfers.

Speed adapters can be either acquired from the emulation vendor or developed in-house. Aldec provides speed adapters for many standard interfaces to enable reliable connectivity with full speed peripherals.

Benefits:

- ICE allows testing with real data streams

- Numerous connectivity options with FPGA prototyping boards

- Peripherals daughter boards can be designed for both emulation and prototyping

- Of the shelf speed adapters are available

In Target Firmware Validation

Co-emulation techniques are indispensable if SoC requires software and firmware validation. Very often abstract virtual models within Virtual Platforms are not accurate enough whereas RTL simulations are orders of magnitude too slow. Co-emulation becomes a key to the successful software validation, productive debugging and complete SoC bring-up.

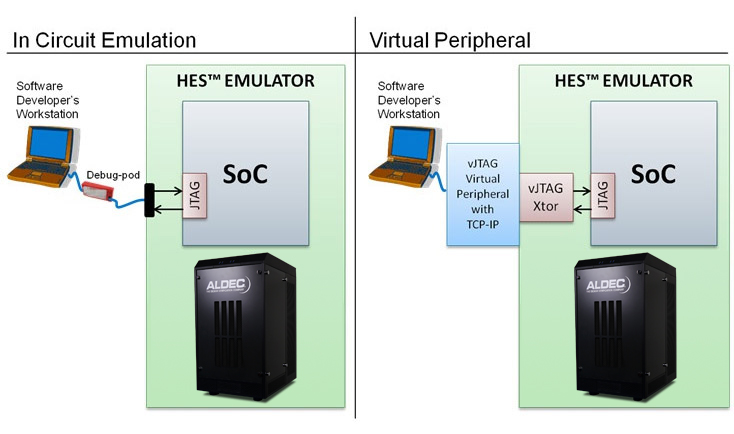

Software developers use software debuggers that may interface with the embedded processor in different ways. This can be either special debugging port or standard JTAG. In any case it is possible using one of the two co-emulation techniques – In Circuit Emulation (ICE) or Virtual Peripheral.

In case of ICE, the JTAG or other debug port is drawn to on-board connector, where dedicated Debug-pod device can be connected. This is a traditional approach that requires only proper connectivity options which is usually a case of FPGA prototyping boards. Interfacing with the emulated JTAG controller of embedded processor is usually straightforward especially if it provides reactive TCK (RTCK) port that allows direct connection without using speed adapters. It is needless to say that ICE based software debugging is fully supported by Aldec’s HES™.

Virtual Peripheral approach is much more flexible. With Aldec’s Virtual JTAG (vJTAG) transactor and Virtual Peripheral that supports TCP-IP it is possible to connect software debugger via LAN. For the time of debugging software that runs in the emulator standing in the Lab, developer can remain at ones desk and workstation. Also no additional Debug-pod devices are required so the platform maintenance is simplified and scalability is enabled.

Another example of virtual peripheral can be ARM® VSTREAM which is also supported in HES™.

Benefits:

- Pre-silicon firmware validation in target hardware

- Hardware / software co-verification

- Choice of either ICE or Virtual Peripheral

- Available proven of the shelf vJTAG transactor

- TCP-IP capable vJTAG Virtual Peripheral enables network access

- vJTAG enables verification platform scalability

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.