Hardware Emulation Solutions

|

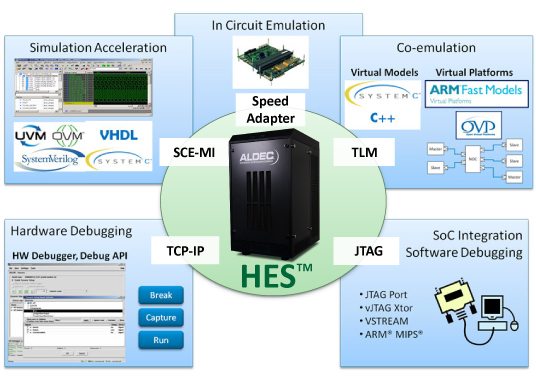

HES-DVM™ is a hybrid verification and validation ecosystem for hardware and software teams developing the latest SoC and ASIC designs. Partnering the latest high-capacity FPGA technology with industry leading co-emulation standards, HES-DVM allows for multiple modes of verification and validation including:

Aldec integrates five main elements within HES™ to provide best-in-class hardware emulation solutions.

Verification IP A complete emulation eco-system must contain a comprehensive library of firm Verification IP (VIP). The availability of transactors, drivers, monitors and speed-adapters of industry leading bus protocols like AMBA AHB, AXI or communication peripherals like USB, PCIe, Ethernet is key to the quick building of a reliable design verification environment and successful deployment of emulation. Aldec provides ready to use VIPs proven in SoC designs that have been already taped-out after successful verification. Aldec’s best experts in the field are ready to develop other VIPs or to assist users with the process.

Debugging Tools HES™ features an array of debugging capabilities such as true RTL view with complete design visibility, memory view/modify, triggering, breakpoints and clock step control. The true RTL view means that all debug probes are saved, preserving original signals’ names, data types and hierarchy. A choice of different waveform formats like ASDB or FSDB allows for integration with either Aldec or 3rd party tools. All debugging functions can be used either within HW Debugger tool or in the testbench via dedicated HES Debug API, with both offering remote access capability via TCP-IP. |

Related Applications

SoC Co-emulationUVM Simulation AccelerationScalability of AccelerationVerification IPSoC PartitioningEmulation Debugging Related Products |

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.