Scalability of Acceleration

Cost-effective FPGA platforms are a great replacement for dedicated emulators due to scalability. With proper software that automates design setup and delivers various interfaces and emulation use models, it is possible to build emulation clusters that have orders of magnitude more computational power than traditional emulators but with a smaller investment. It is important to note that the same FPGA boards can also be reused for prototyping.

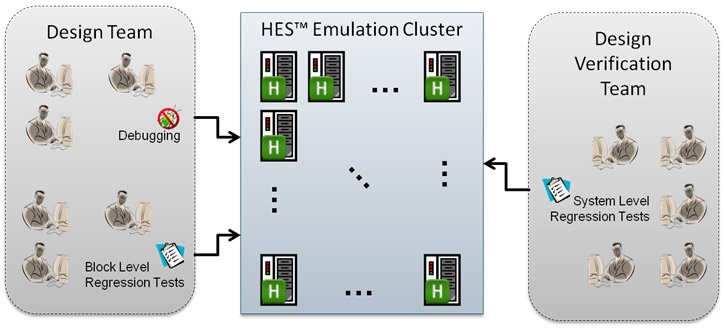

HES-DVM is ideal for building such a powerful infrastructure for both block-level and system-level pre-silicon regression testing. With tens or even hundreds of emulation hosts in the emulation cluster, design engineers can instantly get access to emulators and accelerate block-level simulations. Simultaneously, design verification team can also run comprehensive regression tests of the entire SoC.

HES-DVM-based emulation clusters can be built within standard grid computing systems suc as LSF or SGE. Additionally, remote access to emulation resources can be managed with Aldec’s dedicated tools. Design debugging tools included in HES-DVM connect to emulation targets via Ethernet & TCP-IP, so engineers can access all resources remotely.

Benefits:

- Cost-effective emulation solution can be multiplied

- Easily accessible emulation increases verification productivity at all design stages

- HES-DVM can be used with off-the-shelf prototyping boards and in-house developed FPGA boards

- Networking support facilitates resource sharing and team work

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.