High Frequency Trading

The popularity and value of FPGAs for High Frequency Trading (HFT) systems have increased over the last five years - and the primary reason is latency. HFT firms must utilize the latest technologies in order to achieve close-to-zero latency to remain competitive - whoever has the fastest system wins.

FPGAs consists of millions of logic gates that can process data in parallel as opposed to software that execute data sequentially. Thus, FPGAs can provide deep sub-microsecond latency compared to several microseconds via software. FPGAs includes thousands of DSP blocks that can execute mathematical computations in parallel, and FPGAs are also re-programmable enabling flexible systems that can be optimized even in the field.

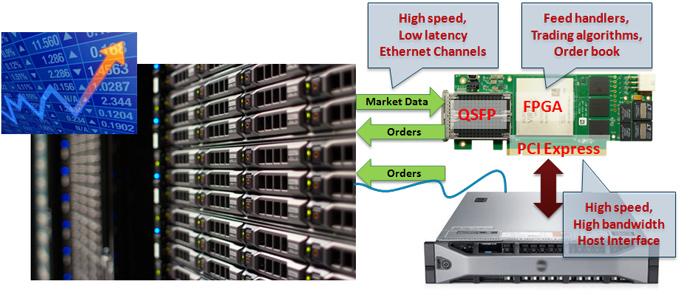

With Aldec’s 30+expertise in FPGA/ASIC prototyping and acceleration, we provide FPGA accelerators with PCIe and QSFP interfaces and compatible with 1U (or larger) trading systems for time-sensitive trading strategies such as Market Making, Statistical Arbitrage and Algorithmic Trading.

Achieving Low Latency

Low latency which is the paramount requirement was achieved by using the newest generation Xilinx FPGA – Virtex™ UltraScale+ and connecting all critical interfaces like Ethernet/QSFP and PCI Express directly to the FPGA. Market data feeds captured directly from the network interface (QSFP) are immediately processed inside FPGA fabric that can accommodate hundreds of parallel processors specialized for a given task. Second QSFP link can be used to trigger buy, sell or cancel orders based on the results of algorithm running entirely in FPGA. Alternatively, pre-processed data can be moved to the host workstation via PCIe interface for analysis in existing software. The pipelining features of FPGA allow for all the interfaces to operate in parallel.

Re-configuration on-the-fly

The FPGA can be re-configured on-the-fly without need of shutting down the entire system which greatly increases the flexibility of such configuration and facilitates quick reaction on dynamically changing trading conditions. The new FPGA accelerators are compatible with 1U and larger trading systems for time-sensitive trading strategies.

Develop and debug FPGA designs

Customers looking for a complete FPGA development eco-system will benefit from cooperation with Aldec with its FPGA accelerator boards and RTL development/simulation tools such as Riviera-PRO – a high performance mixed-language (VHDL/Verilog/SystemVerilog/SystemC) simulator with Python testbench support for FPGAs.

Integrate with IP partners providing IP-cores critical for implementing market data feed handlers and other blocks of the trading system.

Main Features

- Fast processing in newest Xilinx UltraScale+ FPGA

- Higher level speed-grade (-2) of used FPGA

- Low latency interfaces QSFP28

- High bandwidth host interface PCI Express 16x, gen3

- Fast QDR-II memories

- Low profile boards (can be used in 1U rack servers)

- Hot-reconfiguration (FPGA change without power down & PCIe link active)

- Solution vendor with FPGA designing know-how

Solution Contents

- FPGA board, low profile, PCIe, low latency interfaces, 1U-rack server supported

- Riviera-PRO High-Performance Simulator for algorithm development in HDL

- IP-partners for low latency ethernet

- Reference and diagnostic designs with QSFP and PCIe interfaces and QDR-II memory controller

- Integration advisory services

Partner Ecosystem

|

Tamba Networks

|

|

Northwest Logic

|

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.