Compile Xilinx ISE Libraries for Aldec using compxlib

Introduction

NOTE: This App Note is only for Active-HDL 10.1 and older and for Riviera-PRO 2015.02 and older.

To simulate designs that target Xilinx devices, you may need to use Xilinx provided simulation libraries, for example, when your design uses Xilinx primitives, macros or IP cores.

Aldec provides precompiled vendor libraries including Xilinx simulation libraries with our simulators. But in case you would like to compile your own Xilinx simulation libraries, you can use a Xilinx provided utility called compxlib to compile the simulation libraries.

Compiling Xilinx simulation libraries using compxlib

There are three ways to compile Xilinx simulation libraries using compxlib .

Invoke compxlib wizard tool independently

Invoke compxlib from your ISE project

Run compxlib from the command line

This application note shall focus on the first method and use the compxlib GUI independently. With the compilation wizard GUI, the process is very straightforward. Once the simulation libraries are compiled, they can be used for any of your Xilinx designs.

Starting Xilinx Simulation Library Compilation Wizard

You can start the Xilinx Simulation Library Compilation Wizard from Windows's Start menu under Xilinx ISE Design SUITE <version number> -> ISE Design Tools.

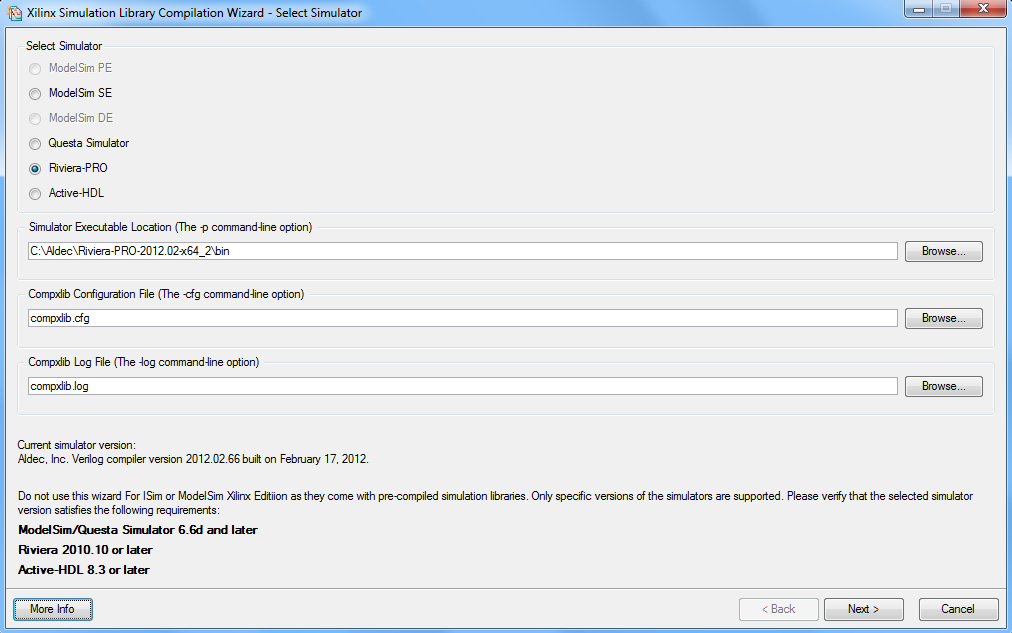

Select Simulator

Once the Xilinx Simulation Library Compilation Wizard opens, you will be asked to select a simulator. For Aldec simulators please select "Riviera-PRO". Please note this will work for both Aldec's Riviera-PRO and Active-HDL.

Please browse and set the executable location for the simulator:

For Riviera-PRO: <Riviera-PRO installation folder>\bin

For Active-HDL: <Active-HDL installation folder>\bin

You may use your own configuration file or log file if you choose to do so. Check the screenshot below for the details:

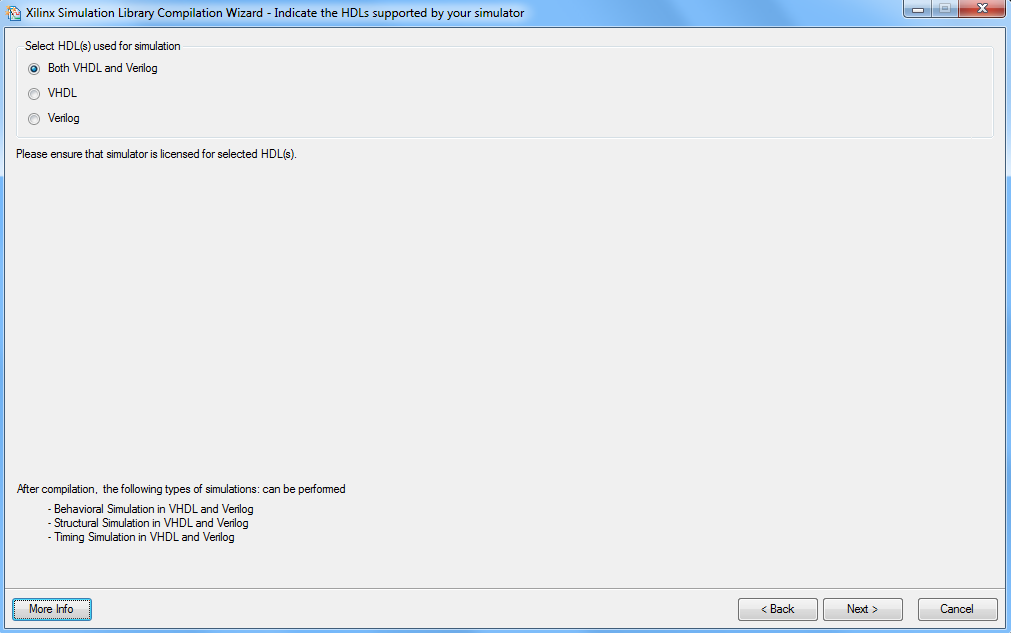

Select HDL language

Next, please select HDL language setting that matches your simulator license. Please note that you may get a simulation initialization error later if you choose to compile a simulation library for an HDL language that you do not have the license for.

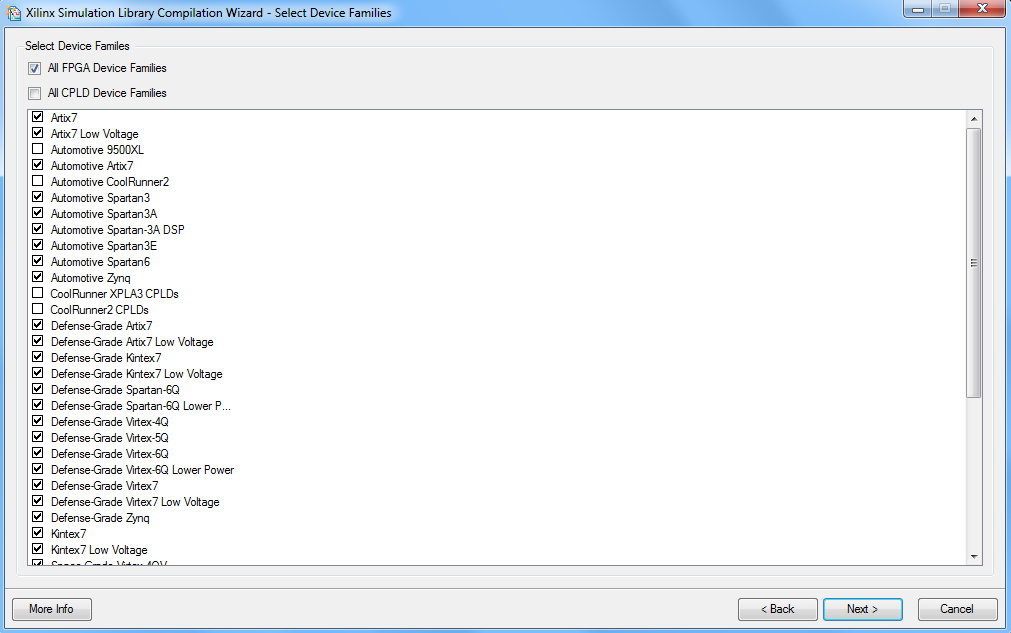

Select Device Families

You will be asked to select Xilinx device families. Since Xilinx primitives and IP cores are device specific, please select devices that you would like to use for your projects.

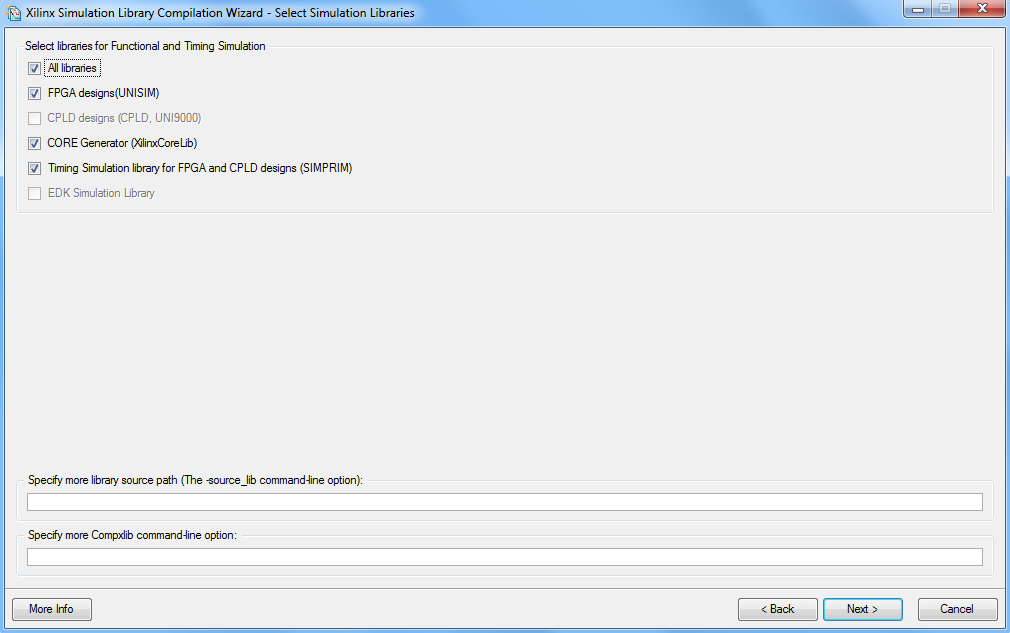

Select Simulation Libraries

Next, you can select what libraries you would like to compile. You can select among FGPA libraries, CPLD libraries, Xilinx CORE libraries or EDK libraries. If you need to specify other library source paths or compxlib command-line options, you can do so at the bottom.

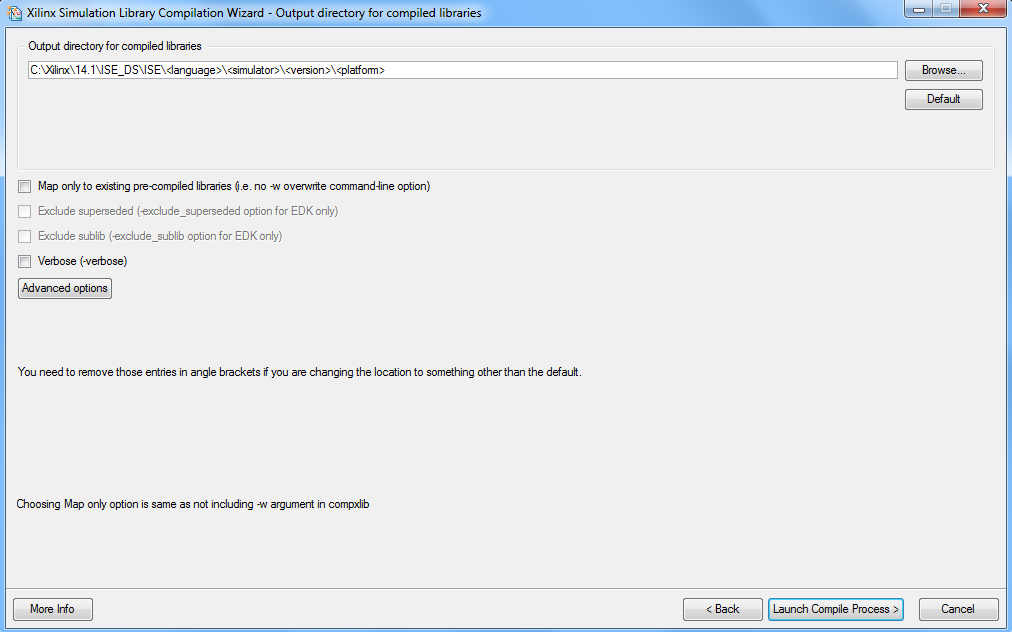

Select Output Directory for Compiled Libraries

Here you can select where you would like to put the compiled simulation libraries.

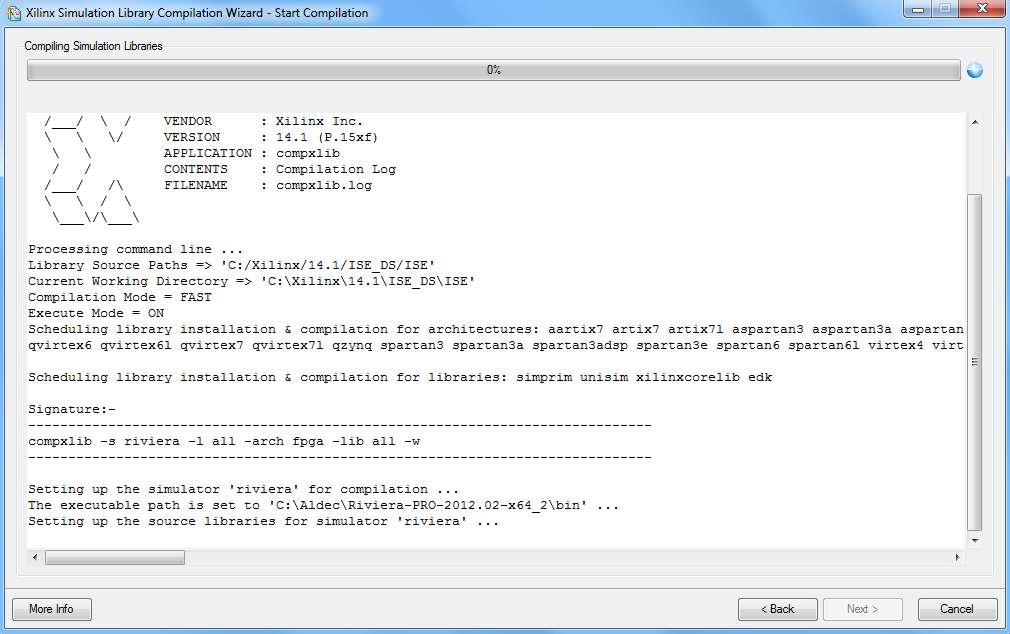

Start Compilation

The compilation will start after you click on the "Launch Compile Process" button:

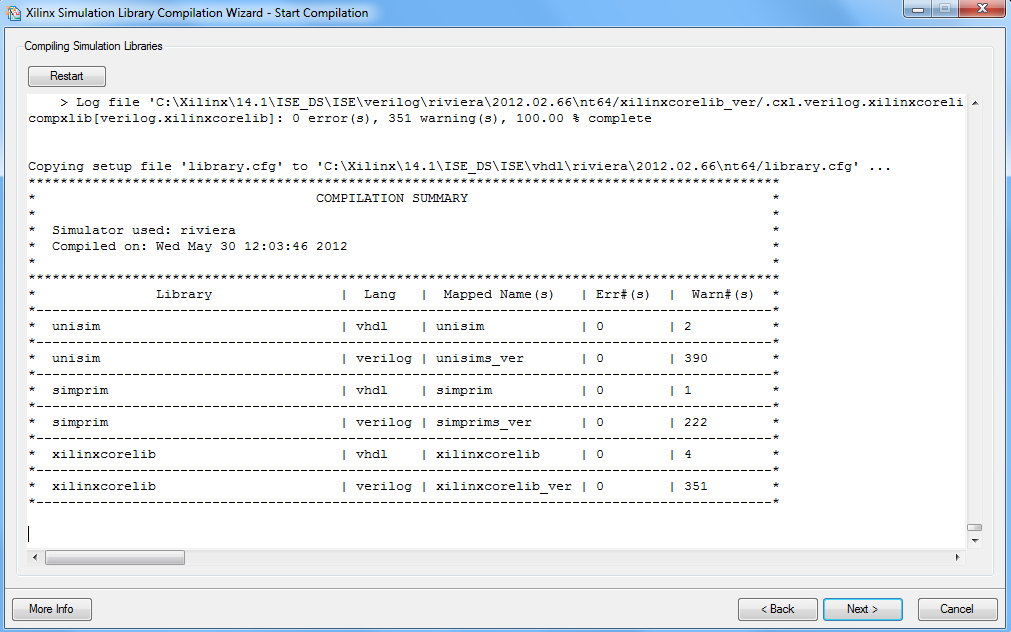

Once it is finished you will receive a report showing the compilation result:

Now you can use the compiled libraries for your Riviera-PRO or Active-HDL designs. Generally, users need to attach the compiled library either through the Library Manager GUI of your Aldec simulator or by using the amap command. Please refer to the online documentation for your simulator or the user manual provided with the software for the details on how to attach the compiled libraries.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.