# Active-HDL™ FPGA Design and Simulation

### **Design Creation and Simulation**

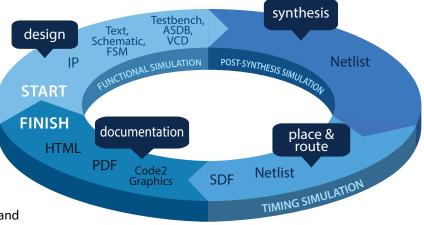

Active-HDL™ is a Windows® based, integrated FPGA Design Creation and Simulation solution for team-based environments. The Integrated Design Environment (IDE) within Active-HDL includes a full HDL and graphical design tool suite and RTL/gate-level mixed language simulator for rapid deployment and verification of FPGA designs.

The design flow manager evokes over 200 EDA and FPGA tools, during design entry, simulation, synthesis and implementation flows and allows teams to remain within one common platform during the entire FPGA development process. Active-HDL supports industry leading FPGA devices from Intel (Altera)®, Lattice®, Microchip®, Quicklogic®, Xilinx® and more.

## **Top Benefits**

- **Unified Team-based Design Management**

- Deploy designs quickly with Text, Schematic and **State Machine**

- Powerful common kernel mixed-language simulator (VHDL, Verilog, SystemVerilog/UVM, and SystemC)

- Advanced Debugging and Code Coverage

- Assertion-Based Verification (SVA, PSL)

- DSP Co-simulation with MATLAB®/Simulink® interface

- Share designs quickly with auto-generate Design **Documentation in HTML and PDF**

#### Design

The Design Suite within Active-HDL utilizes graphical and textual design entry methods, and integrates over 200 EDA tools into a single platform. Design management tools help eliminate issues faced by team-based designs during the FPGA developement process.

#### Debug

Active-HDL incorporates a common kernel mixed-language simulator with interactive tools that enables designers to debug quickly. Debugging tools such as Advanced Data Flow and Xtrace provide users a graphical representation of the system's internal signals increasing observability and aiding in the debug of large designs. Active-HDL also includes Code Coverage and Analysis tools, allowing designers to incorporate metric-driven verification into the design process.

#### Document

Active-HDL allows designers to quickly document all aspects of their design workspace for later review, reuse, and archiving. This enables the ability to maintain proper documentation at all stages of the development process, eliminating many issues faced by multi-team design environments.

STANDARDS -

SILICON

INTERFACES -

cādence

SYNOPSYS°

#### FEATURES PRODUCT CONFIGURATIONS

| FEATURES                                                                                       | PRODUCTO   | PRODUCT CONFIGURATIONS |             |          |

|------------------------------------------------------------------------------------------------|------------|------------------------|-------------|----------|

| Design Entry and Documentation                                                                 | DM         | DE                     | PE          | EE       |

| HDL, Text, Block Diagram and State Machine Editor                                              | •          | •                      | •           | •        |

| Language Assistant with Templates and Auto-Complete                                            | •          | •                      | •           | •        |

| Macro, Tcl/Tk, Perl script Support                                                             | •          | •                      | •           | •        |

| Mouse Strokes                                                                                  | •          | •                      | •           | •        |

| Code2Graphics™ Converter                                                                       | •          |                        | •           | •        |

| Legacy Schematic Design Import and Symbol Import/Export                                        | •          |                        | •           | •        |

| Export to PDF/HTML/Bitmap Graphics                                                             | •          |                        | •           | •        |

| Project Management                                                                             |            |                        |             |          |

| Design Flow Manager for All FPGA Vendors                                                       | •          | •                      | •           | •        |

| Revision Control Interface                                                                     | •          | •                      | •           | •        |

| Team-based Design Management                                                                   | •          | •                      | •           |          |

| PCB Interface                                                                                  |            |                        | •           | •        |

| Code Generation Tools                                                                          |            |                        |             |          |

| IP Core Component Generator                                                                    |            |                        | •           |          |

| Testbench Generation from Waveforms                                                            |            |                        | •           | •        |

| Testbench Generation from State Diagram                                                        |            |                        | •           |          |

| Supported Standards                                                                            |            |                        |             |          |

| VHDL IEEE 1076 (1993, 2002, 2008 and 2019)                                                     | •          | •                      | •           | •        |

| Verilog® HDL IEEE 1364 (1995, 2001 and 2005)                                                   |            | •                      |             | •        |

| SystemVerilog IEEE 1800™-2012 (Design)                                                         | •          |                        |             |          |

| EDIF 2 0 0                                                                                     |            |                        |             |          |

| SystemC™ 2.3.1 IEEE 1666™/TLM 2.0                                                              |            |                        | Option      |          |

| SystemVerilog IEEE 1800™-2012 (Verification)                                                   |            |                        | -           | Option   |

| Simulation/Verification                                                                        |            |                        |             |          |

| Simulation Performance                                                                         |            | - D I:                 | 2           | Up To 9x |

| (Baseline 2X Faster than FPGA Vendor Supplied Simulator)                                       |            | Baseline               | 3× Baseline | Baseline |

| Single or Mixed Language Design Support                                                        | Mixed Only | Mixed Only             |             | •        |

| Simulation Model Protection/Library Encryption                                                 |            | •                      | •           | •        |

| VHDL/Verilog IEEE Compatible Encryption                                                        |            | •                      | •           |          |

| Value Change Dump (VCD and Extended VCD) Support                                               |            | •                      | •           |          |

| Verilog Programming Language Interface(PLI/VPI)                                                |            | •                      | •           |          |

| VHDL Programming Language Interface (VHPI)                                                     |            |                        | •           |          |

| Batch Mode Simulation/Regression (VSimSA)                                                      |            |                        | •           | •        |

| Pre-compiled FPGA Vendor Libraries                                                             | •          | •                      | •           |          |

| Xilinx SecureIP Support                                                                        |            | •                      | •           | •        |

| Intel® Language-Neutral Libraries                                                              |            | •                      | •           | •        |

| Microchip® Language-Neutral Libraries                                                          |            | •                      | •           | •        |

| Profiler (Performance Metrics)                                                                 |            |                        | Option      | •        |

| SFM (Server Farm Manager)                                                                      |            |                        | Option      | Option   |

| 64-bit Simulation                                                                              |            |                        | •           |          |

| Traceability from Requirements to HDL Source Code                                              | Option     | Option                 | Option      | Option   |

| HDL Debug and Analysis                                                                         |            |                        |             |          |

| Interactive Code Execution Tracing                                                             |            | •                      | •           | •        |

| Advanced Breakpoint Management                                                                 |            | •                      |             | •        |

| Memory Viewer                                                                                  |            | •                      | •           |          |

| Waveform Viewer                                                                                |            |                        |             |          |

| Waveform Stimulator                                                                            |            |                        |             |          |

| Waveform Comparison and Editing                                                                |            |                        |             | •        |

| Post-Simulation Debug                                                                          |            |                        |             |          |

| C++ Debugger                                                                                   |            |                        |             |          |

| Signal Agent (VHDL and Mixed Only)                                                             |            |                        |             |          |

| X-Trace                                                                                        |            |                        |             |          |

| Advanced Dataflow                                                                              |            |                        |             |          |

| Integration with Riviera-PRO and ALINT-PRO                                                     | Option     |                        | Option      |          |

| Assertions Debugging                                                                           |            |                        | Option      |          |

| Assertions and Coverage Tools                                                                  |            |                        | - partie    |          |

| Code, Statement, Branch, Expression, Condition, Path, Toggle Coverage, and Functional Coverage | e          |                        | •           |          |

| PSL IEEE 1850, SystemVerilog IEEE 1800™                                                        |            |                        | Option      |          |

| Design Rule Checking                                                                           |            |                        | орион       | ·        |

| ALINT™-PRO with Aldec Basic Rule Library                                                       |            |                        | Option      | •        |

| DO-254 VHDL or Verilog Rule Library                                                            |            |                        | Option      | Option   |

| STARC® VHDL or Verilog Rule Library                                                            |            |                        | Option      |          |

|                                                                                                |            |                        |             | Option   |

| RMM Verilog and VHDL Rule Library Co Simulation                                                | _          |                        | Option      | Option   |

| Co-Simulation                                                                                  |            |                        | •           |          |

| Simulative Co. Simulation                                                                      |            |                        | •           | •        |

| Simulink® Co-Simulation                                                                        |            |                        | 0           |          |

| MATLAB® Co-Simulation                                                                          |            |                        | Option      | •        |

|                                                                                                |            |                        | Option      |          |

Aldec, Inc.

Ph +1.702.852.4000

sales@aldec.com

Visit us at www.aldec.com