会社概要

アルデック(Aldec, Inc.)は業界をリードするEDAツール・ベンダとして、革新的なデザイン作成、シミュレーション、検証ソリューションをリリースし、大規模FPGA/ASIC/SoCや組み込みシステム・デザインの開発に採用されています。プロダクトラインの表示(pdf)

使用中のユーザは3万5000人以上、全世界にパートナー50社以上です。全世界にオフィスを構え、43ヶ国に販売網を拡げ、デザイン検証の分野で確固たる実績があります。

市場

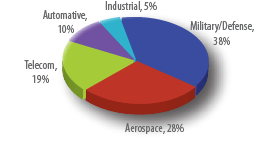

アルデックの世界市場シェアはFPGA向けの混合言語RTLシミュレータの分野で38%です(FPGAメーカから直販のOEMシミュレータを除く)。

アルデックの進出している分野は、政府関係、軍事、航空宇宙、通信、自動車、その他安全が重視される分野などです。主要なユーザには、IBM, GE, Qualcomm, Texas Instruments, Applied Micro, Hewlett Packard, 東芝, Intel, NEC, 三菱, LG, 日立, NASA, Invensys, Westinghouse, Raytheon, パナソニック, Lockheed Martin, Samsung(順不同)が含まれます。

また数多くの新進ベンチャー企業および各種・教育機関等にご利用頂いています。アルデックのEDA検証ツールのユーザはデザインのパフォーマンス・アップや開発期間短縮、コスト削減に成功しています。

アルデック・ジャパン株式会社 概要

- 社名: アルデック・ジャパン株式会社

(英文名 Aldec Japan K.K.) - 所在地: 〒160-0023 東京都新宿区西新宿3-3-13

西新宿水間ビル 6F - 設立: 2007年4月2日

- 資本金: 1,500万円

- 代表者: 代表取締役 ダグマラ・ハイデューク

- 取引銀行: 三菱東京UFJ銀行 麹町中央支店

- 業務内容: 米国アルデック社製品の日本国内における販売、技術サポート、保守業務

- 取扱製品: Active-HDL、Riviera-PRO、ALINT、ALINT-PRO-CDC、HES-7、HES-DVM 他

- 個人情報の取り扱いについてはこちらをご参照ください

特許技術

- US Patent#4,791,357: Electronic circuit board testing system and method

- US Patent#4,827,427: Instantaneous incremental compiler for producing logic circuit

- US Patent#5,479,355: System and method for closed loop operation of schematic designs with electrical hardware

- US Patent#5,051,938: Simulation of selected logic circuit designs

- US Patent#6,578,133: MIMD Array of Single Bit Processors for Processing Logic Equations in Strict Sequential Order

- US Patent#6,915,410: Compiler synchronized multi-processor programmable logic device with direct transfer of computation results among processor

- US Patent#7,003,746: Method and apparatus for accelerating the verification of application specific integrated circuit designs

沿革 |

|

| 2021 | |

|

|

| 2020 | |

|

|

| 2019 | |

|

|

| 2018 | |

|

|

| 2017 | |

|

|

| 2016 | |

|

|

| 2015 | |

|

|

| 2014 | |

|

|

| 2013 | |

|

|

| 2012 | |

|

|

| 2011 | |

|

|

| 2010 | |

|

|

| 2009 | |

|

|

| 2008 | |

|

|

| 2007 | |

|

|

| 2006 | |

|

|

| 2005 | |

|

|

| 2004 | |

|

|

| 2003 | |

|

|

| 2002 | |

|

|

| 2000 | |

|

|

| 1999 | |

|

|

| 1997 | |

|

|

| 1996 | |

|

|

| 1992 | |

|

|

| 1985 | |

|

|

| 1984 | |

|

|

Aldec, Inc.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.

Printed version of site: support.aldec.com/jp/company