HES-VU19PD-ZU7EV

キャパシティ

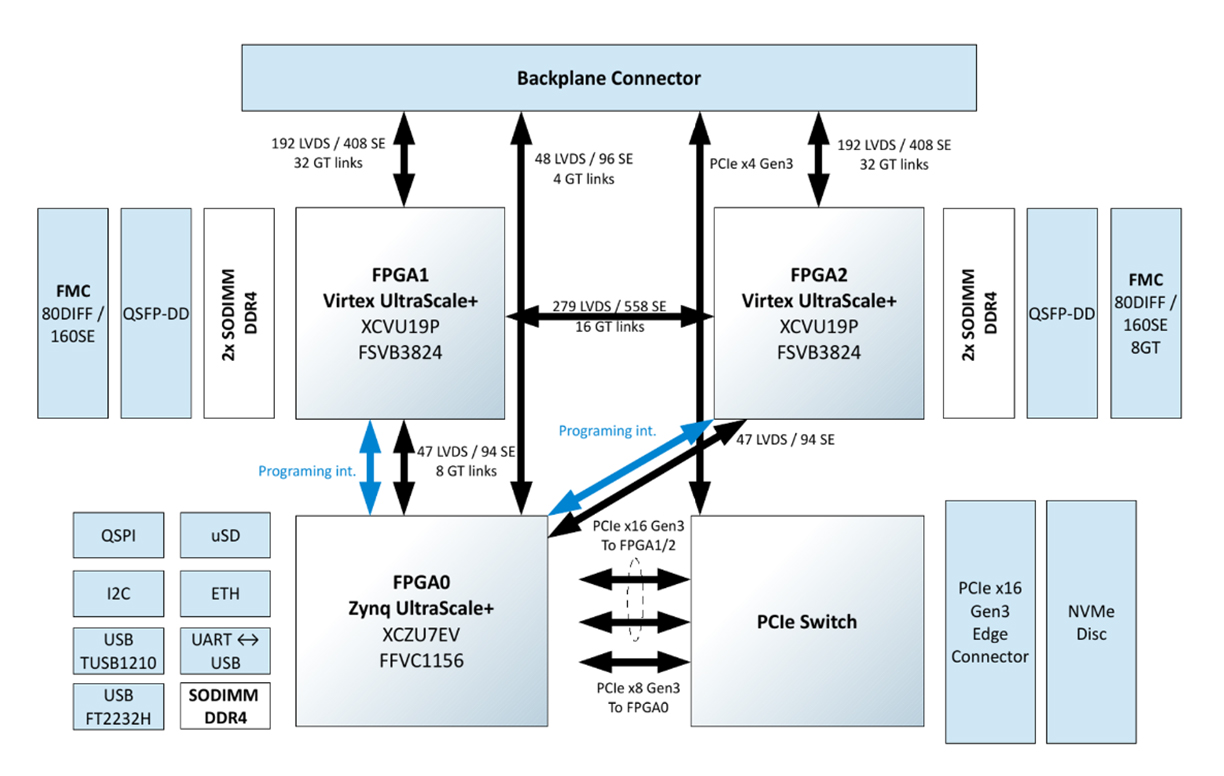

HES-VU19PD-ZU7EVは、ロジックモジュールとしてVirtex UltraScale+ VU19P FPGAを2個、ホストモジュールとしてXilinx Zynq UltraScale+ ZU7EV MPSoCを1個搭載したユニークな組み合わせで、クアッドコアのARM® Cortex-A53、デュアルコアのARM® Cortex-R5リアルタイムプロセッシングユニット、ARM® Mali-400 MP2 GPU、統合されたH.264/H.265ビデオコーデック、UltraScale+™プログラマブルロジックを備えています。 このボードは、中規模から大規模のASICデザインの高速フィジカルプロトタイピングおよびエミュレーションをターゲットとしています。HES-VU19PD-ZU7EVは83MASICゲートを提供し、バックプレーンを介して最大316Mゲートになります。

ボード上には5つのSODIMM外部メモリが用意されており、4つはVU19Pデバイスに1つはZU7EVデバイスに接続されています。VU19Pデバイスのオンチップメモリは166Mb、ZU7EVデバイスは11Mbです。

| Resources | VU19P Virtex UltraScale+™ FPGA |

ZU7EV Zynq UltraScale+™ MPSoC | |

| Logic Cells/LUTs (K) | 8,938 | 504 | |

| Total Block RAM (Mb) | 75.9 | 11 | |

| UltraRAM (Mb) | 90 | 27 | |

| DSP Slices | 3840 | 1728 | |

| Transceivers | 80 GTY (32.75 Gb/s) | 20 GTH (16.3Gb/s) | |

| I/O | 1664 HP, 96 HD | 214 PS, 312 HP, 48 HD | |

クロッキング

2つの設定可能なクロックジェネレーター(PLL)、FPGA0-2(XCZU7EV)GTHトランシーバー用の2つのリファレンスクロック、FPGA0-2用の100MHzと200MHzの2つのリファレンス発振器、FPGA1-2(XCVU19P)用の400 MHzのリファレンス発振器、および接続された基準発振器があります。 HES-XCVU19PD-ZU7EVボード上のSODIMMメモリ専用のFPGA1-2へ。 さらに、FPGA0-2、FMC、およびHES-XCVU19PD-ZU7EVボード上のSODIMMメモリ専用のFPGA1-2に接続された基準オシレータがあります。 さらに、FPGA0-2、FMC、およびBPコネクタ間でクロックを分配できるようにする6つのクロックバッファが搭載されています。

ホスティングとインタフェース

このボードは、ボードのPCIe x16エッジコネクタを介してワークステーションやサーバーに接続されます。FPGAデバイスに接続するための多様なインターフェースを利用できます。

| Interfaces | |

| Virtex® UltraScale+™ VU19P FPGA | Zynq® UltraScale+™ ZU7EV MPSoC (connected to the ARM® processing system) |

|

|

ボード上のFPGAの他に、接続されているすべてのデバイス(ZynqおよびVU19Pデバイス)とNVMe SSDカードとの間の通信を準備する役割を担うPCIe スイッチデバイスがあります。VU19P FPGAには16リンク、Zynq MPSoCには8リンク、そしてPCIe x4 Gen3のバックプレーンコネクタが接続されています。

アルデックは、プログラミングとボードとの通信に必要なドライバとユーティリティを含むHES Proto-AXIソフトウェアパッケージを提供します。アルデックは、ホスト接続を素早く立ち上げるために、ZU7EVデバイスとHES Proto-AXIソリューション用の組み込みLinuxのイメージをすぐに使用できるようにしています。このソリューションは、AMBA AXIインタフェースを備えたブリッジモジュールIPと、LinuxおよびWindows PC用のC++ APIを備えた付属のPCI Express HESドライバで構成されており、ブリッジの背後にあるAMBA AXIローカルバスに直接データを転送することができます。HES-VU19PD-ZU7EVは、HES Proto-AXI組み込みモードをサポートしており、このボードはワークステーションとのPCIe接続なしにスタンドアロンモードで機能します。電源は、標準の6ピンPCIe電源ケーブルで供給されます。

HES-VU19PD-ZU7EV

FPGA & Capacity

- Main FPGA: 2x Virtex UltraScale+ XCVU19P-FSVB3824 (1664 HP, 96 HD and 80 GTY)

- ASIC Gates estimated:

- 83 Million Gates single board

- 332 Million Gates with four boards in a backplane

- Host FPGA: Zynq UltraScale+ XCZU7EV-FFVC1156 (214 PS, 312 HP, 48 HD)

Flexible Clocking

- Two configurable clock generators (PLL) provide 2 clocks for FPGA0-FPGA2 and backplane and 2 clocks for FPGA1-FPGA2 and backplane

- Two reference oscillators 100MHz and 200MHz for FPGA0-FPGA2

- 400MHz reference oscillators for FPGA1-FPGA2

- 200MHz reference oscillator for SODIMM memory to FPGA1-2

- Six clock buffers (distribution clocks between FPGA, FMC and backplane connectors)

- Two reference clocks for GT links

- Additional dedicated clock source for PCIe and QSFP interfaces

Connectivity & Expandability

- Full size backplane connector

- Daughter card connectors (FMC-HPC)

- Standard FPGA Mezzanine Card connectors

- Compliant with ANSI/VITA 57.1 FMC Standard

- 2 FMC sockets connected to UltraScale+ FPGAs

- FMC1 (80 DIFF / 160 SE, 8 GT)

- FMC2 (80 DIFF / 160 SE)

- Inter-FPGA connections

- UltraScale interconnections

- 279 Diff - standard GPIO optimized for LVDS

- 16 GT - high speed serial I/O

- UltraScale to ZU7EV host FPGA connections

- 47 Diff - standard GPIO optimized for LVDS

- 8 GT - high speed serial I/O

- GPIO & Misc

- 4x USER LEDs

Memory Resources

- Up to 64 GB of DDR4

- 4 DDR4 SO-DIMM slots

- 2 slots and up to 16 GB per VU19P

- Memories connected to Zynq MPCoC UltraScale+

- 1 SO-DIMM slot

- QSPI Flash

- Micro-SD slot for memory to store FPGA configuration bit-files

- NVMe disc interface (connected to FPGA0-FPGA2 via pcie switch

Interfaces & Hosting

- Host interfaces at VU19P

- PCIe interface for each FPGA

- Fixed PCIe x16 gen3

- PCIe Switch

- 2x QSFP-DD

- Interfaces at ZU7EV

- uSD

- 1 Gb Ethernet

- UART

- USB

- I2C

- Board configuration and FPGA programming

- Aldec’s Board Configuration Controller loaded in Zynq ZU7EV

- Programming from Host

- via USB 2.0 (Aldec HES Proto-AXI application)

- via JTAG (Xilinx utilities)

- Programming from Micro-SD card

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.