HES-XCVU9P-ZU7EV

プロダクトの詳細

キャパシティ

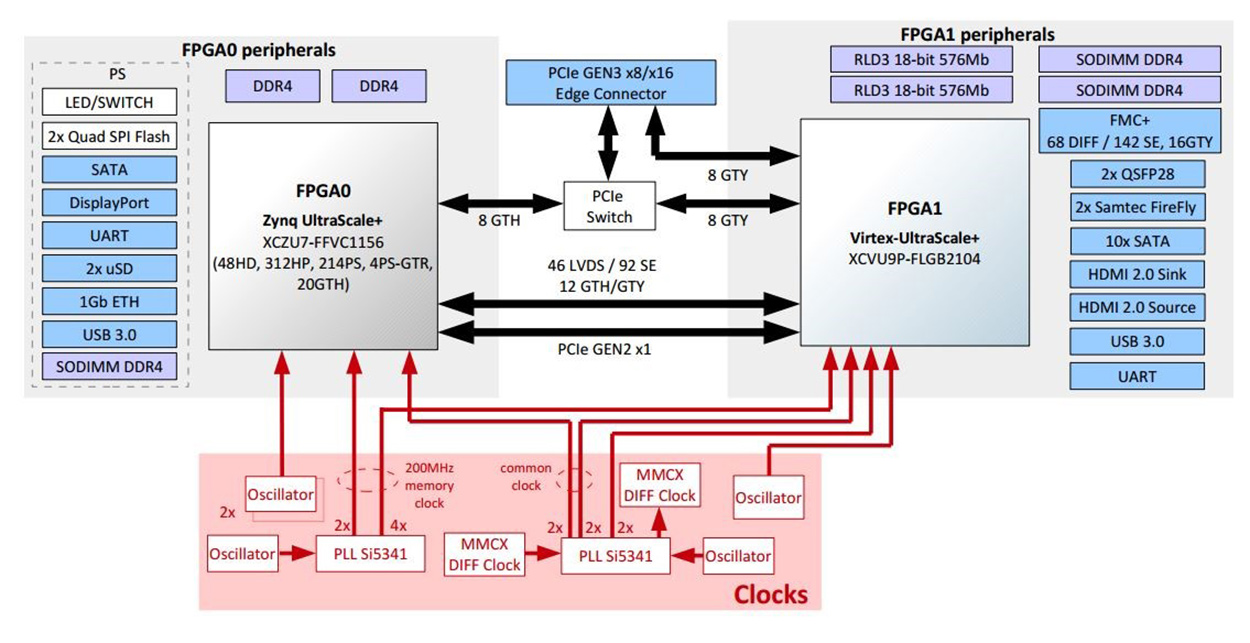

HES-XCVU9P-ZU7EVは、巨大なデジタル信号処理を必要とする高性能コンピューティング(HPC)アプリケーション用に設計されています。 このボードは、 ZU7EV Zynq® UltraScale+™ MPSoCとVU9P Virtex® UltraScale+™を独自に統合しています。この異種コンピューティングプラットフォームは、クアッドコアの ARM® Cortex-A53、デュアルコアのARM® Cortex-R5リアルタイム処理ユニット、ARM® Mali-400 MP2 GPU、統合H.264 / H.265ビデオコーデック、および16nm FinFETノードのUltraScale+™プログラマブルロジックを利用しています。

利用可能なオンボード外部メモリリソースには、3つのDDR4 SODIMMスロットと2つの576Mb RLDRAM-3モジュール(合計1Gb)があります。Zynq® プログラマブルロジック用のオンチップメモリには、11MbのブロックRAMと27MbのUltraRAMが含まれています。 VU9Pプログラマブルロジック用のオンチップメモリは75.9MbのブロックRAMと270MbのUltraRAMを含みます。

| Resources | VU9P Virtex UltraScale+™ FPGA | ZU7EV Zynq UltraScale+™ MPSoC |

|

Logic Cells/LUTs (K) |

2586 | 504 |

|

Total Block RAM (Mb) |

75.9 | 11 |

|

UltraRAM (Mb) |

270 | 27 |

|

DSP Slices |

6840 | 1728 |

|

Transceivers |

76 GTY 32.75 Gb/s | 20 GTH 16.3Gb/s |

|

I/O |

702 HP | 214 PS, 312 HP, 48 HD |

クロッキング

クロッキングは、オシレータ、PLL、およびMMCXコネクタによって提供されます。 専用の発振器は、オンボードPLLと同様にFPGAデバイスに直接接続されています。 オンボードPLLは、FPGAデバイス用に任意周波数の共通クロックと様々なアプリケーションに対応するためのVU9Pへの専用の任意周波数のクロックを提供します。 FMC+コネクタの13差動クロック入力を介して、VU9Pへクロックを供給することも可能です。

ホスティングとインタフェース

ボードは、ワークステーションまたはサーバーにボードのPCIe x16エッジコネクタを介して接続されています。 FPGAデバイスに接続するために多種多様なインターフェースが利用可能です。

| Interfaces | |

| VU9P Virtex® UltraScale+™ FPGA | ZU7EV Zynq® UltraScale+™ MPSoC (connected to the ARM® processing system) |

|

|

Aldecは、Hes.Asic.Protoソフトウェアパッケージに、プログラミングとボードとの通信に必要なドライバとユーティリティを提供しています。ホスト接続の素早い立ち上げのために、Aldecはすぐに使用できるZU7EVデバイス用の組み込みイメージとHES Proto-AXIソリューションを提供します。これはAMBA AXIインタフェースを備えたブリッジモジュールIPと、LinuxおよびWindows PC用のC++ APIを備えたPCI Express HESドライバで構成されており、ブリッジの後にあるAMBA AXIローカルバスに直接データを転送できます。電源は標準の6ピンPCIe電源ケーブルで供給されます。

HES-XCVU9P-ZU7EV

FPGA & Capacity

- Main FPGA: Virtex UltraScale+ XCVU9P-FLGB2104 (I/O: 702 HP, 76 GTY)

- Host FPGA: Zynq UltraScale+ XCZU7EV-FFVC1156 (I/O: 214 PS, 48 HD, 312 HP, 20 GTH)

Flexible Clocking

- Two (2) dedicated any-frequency clocks to VU9P

- Two (2) common any-frequency clocks to VU9P and ZU7EV

- Dedicated oscillators for VU9P and ZU7EV

- Thirteen (13) differential clock inputs from FMC+ to VU9P

Memory Resources

- Memories connected to the VU9P

- 2x 18-bit 576 Mb RLDRAM-3 modules (1Gb total)

- 2x SODIMM DDR4 slots

- Memories connected to the ZU7EV

- 2x 4Gb DDR4 modules (8Gb total)

- 1x SODIMM DDR4 slot

- 2x 512Mb Quad SPI Flash (1Gb total)

Interfaces & Hosting

- Host interfaces connected to ZU7EV

- PCIe 3.0 x8

- SATA

- DisplayPort

- UART

- 2x MicroSD

- 1Gb Ethernet

- USB 3.0

- Host interfaces connected to VU9P

- PCIe 3.0 x8/x16

- FMC+ (68 DIFF / 142 SE, 16 GTY)

- 2x QSFP28

- 2x Samtec Firefly

- 10x SATA (8x HOST and 2x DEVICE)

- HDMI 2.0 Sink

- HDMI 2.0 Source

- USB 3.0

- UART

- Hosting

- Aldec HES Proto-AXI drivers and programming utilities

Miscellaneous

- USB 3.0, uSD card socket and QSPI Flash memory for configuration

- 2x 4Gb DDR4 and DDR4 SO-DIMM socket for control FPGA

- DisplayPort connected to control FPGA

- SATA connected to control FPGA

- 1Gb Ethernet connected to control FPGA

- UART interface connected to control FPGA

- Power supply voltages supervisor

Software Support

- Full integration with Aldec HES/DVM

- Full support for Xilinx Chipscope debug and embedded logic analyzers via JTAG

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2024 Aldec, Inc.