グラフィカル/テキスト・デザインエントリ

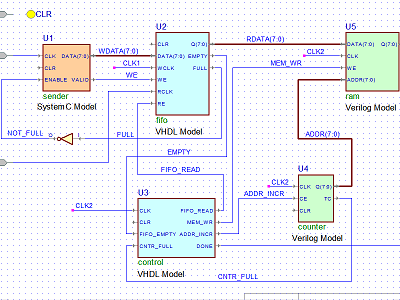

スケマティック / ブロック・ダイアグラム・エディタ

ブロック・ダイアグラム・エディタはVHDL, Verilog, EDIFデザインをグラフィカルに入力できるツールです。HDLデザインの大部分が構造化されていれば、ソースコードで入力するより、ブロック・ダイアグラムとして記述する方が簡単なことが多いです。エディタで入力したダイアグラムは、ブロック・ダイアグラム・エディタが自動でVHDLかVerilogまたはEDIFネットリストに変換します。Active-HDLでは、ブロック・ダイアグラムとソースコードを混在させて利用することもできます。例えば、トップレベルのデザインエントリはブロック・ダイアグラムで、トップレベルの中にインスタンス化されるコンポーネントはHDLコードやEDIFネットリストやステート・ダイアグラムで記述することができます。

スケマティック・エディタのメリット

- ボトムアップの手法もトップダウンの手法もともにサポート

- ベンダ用のスケマティック・ライブラリでテクノロジーに合わせたブロック・ダイアグラムが作成可能

- エディタは階層を扱えるので、複雑なブロックのスケマティックを複数ページに分割可能

- ブロック・ダイアグラム・ファイルをVHDL, Verilog, EDIFネットリストに変換可能

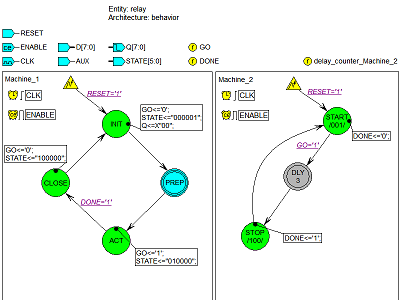

ステート・マシン・エディタ

ステート・マシン・エディタは同期マシン・非同期マシンのステート・ダイアグラムのグラフィカルな編集ができるツールです。ステート・ダイアグラムは、従来の順序回路のモデリングに代わる記述方法です。自分自身でHDLコードを書くのではなく、論理ブロックでグラフィカルなステート・ダイアグラムを作成すれば、その記述に基づいて、エディタが自動でHDLコードを生成します。ステート・ダイアグラムは直感的に分かる図形式なので、HDLコードより習得しやすく、かつ読むのもずっと楽です。

ステート・マシン・エディタのメリット

- ステートからステートへのフロー、イベント、アクションなどを視覚的に表現できるので、読みやすく理解しやすい

- 組込のテストベンチ・ジェネレータでステート・マシンをすぐに検証可能

- 設計会議の際、コラボレーション・ツールとして、デザインを理解・説明しやすく図示することができる

- 色々な抽象レベルでデザインを文書化する際に役立つ

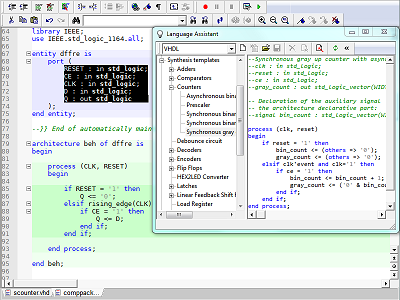

HDLテキスト・エディタ

HDLエディタはHDLソースコード編集用のエディタです。コンパイラとシミュレータと緊密に連携して、デバッグすることができます。HDLテキスト・エディタの主要機能としては、キーワードのハイライト(VHDL, Verilog/SystemVerilog, C/C++, SystemC, OVA, PSL)、コードのグループ化とコード構造をサポート、オートコンプリートとオートフォーマット、ソースコードのナビゲーション用のブックマークとタグ付きブックマーク、ブレークポイント、および列選択などがあります。

HDLテキスト・エディタのメリット

- 波形ビューワとHDLテキスト・エディタのクロス・プロービングでスムーズなデバッギング

- HDLエディタから波形ビューワに信号を直接挿入可能

- シミュレーション中にソースコードの値をライブ・プローブ可能

- コード記述の助けとなるVHDL, Verilog, SystemVerilog, SystemCの言語テンプレート

コード・トゥ・グラフィックス

コード・トゥ・グラフィックス・コンバータはVHDL, Verilog/SystemVerilogおよびEDIFネットリストをActive-HDLのスケマティックとステート・ダイアグラムに変換するツールです。VHDL, Verilog/SystemVerilog, EDIFのファイルを解析して、発見されたエンティティ、モジュール、セルの数に応じて、スケマティックとステート・ダイアグラムのファイルを生成します。生成したスケマティック・ファイルとステート・ダイアグラム・ファイルはデザインの中に入れることもできますが、別の場所に保存することもできます。

コード・トゥ・グラフィックスのメリット

- デザインから情報を抽出し、グラフィカルに表現

- RTLデザインをグラフィカルに視覚化することでデザイン再利用プロセスを大きく拡張

- 大規模なRTLデザイン・プロジェクトでも完全なドキュメンテーション化が可能

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.