シミュレーションおよびデバッグ

SystemVerilogシミュレーション

SystemVerilogはIEEEの認証を受けた(IEEE 1800™)言語で、前身であるVerilog HDLよりも大きく向上させることができるようになりました。SystemVerilogはVHDL, VerilogそれにC++の長所を多く採り入れ、システム・アーキテクチャ、設計および検証をする上で非常に優れた特徴を備えています。

SystemVerilogは大きく3つの部分に分かれます。その3つとは、ハードウェア記述、アサーション、テストベンチ言語です。ツールとライセンスの設定によって、この3つの部分の機能のうち利用できる部分が異なります。(無料のSystemVerilogチュートリアルをご覧になりたい方はここをクリック)

SystemVerilogベースのUniversal Verification Methodology(UVM)はAccellera認定のファンクショナル・ベリフィケーションの手法で、業界でもすでに定評があります。アルデックはコンパイル済みのUVMライブラリとSystemVerilogシミュレータを提供し、今日の大規模・複雑なデザインの検証課題に対応します。

VHDL 2008シミュレーション

言語規格のVHDL IEEE 1076-2008は前バージョンに強力な機能を加え、同時にユーザーフレンドリーになりました。VHDL-2008では検証と設計において重要な言語拡張が行われ、多くの新機能から色々なメリットがあります。例えばPSLの取り込み(プロパティとアサーションのサポート)、IP保護(暗号化ファイルのコンパイル)、VHPI、固定小数点および浮動小数点パッケージ、ジェネリック・パッケージ、新規タイプ(integer_vector, boolean_vectorなど)、組み合わせロジックの処理、条件文とcase文の簡略化、代入の拡張、演算子の追加・拡張、ビット列リテラルの拡張、ポートマップの拡張、コンテキスト宣言とコンテキスト文などです。VHDL IEEE 1076-2008はVHDL IEEE 1076-1993以来、VHDLにおいて最大の言語拡張でした。

アルデックはメンテナンス契約が有効でVHDLまたは混合言語シミュレーションが使用可能なお客様には、追加費用なしでActive-HDL™とRiviera-PRO™の両方でVHDL-2008のサポートを提供しています。

SystemC協調シミュレーション

SystemCはC++を用いてデジタル・システムの記述と検証をするための環境です。SystemCは元々はOSCI(Open SystemC Initiative)が開発し、現在はIEEE 1666™-2005の管理下にある言語ですが、標準のC++にはない、ハードウェアやシステムに関連した機能を提供するクラスおよびテンプレートのライブラリです。

Active-HDLとRiviera-PROの両方でC/C++とSystemCをサポートし、さらにどちらのシミュレータもHDLコードとC言語の特徴をシームレスに統合できます。IEEEで規格化されたインタフェースを用いることで、HDLモデルをハイレベルのC言語テストベンチでシミュレーションしたり、CモデルをHDLの中にインスタンスしたり、ビジュアライゼーション・ソフトウェアをHDLに接続したり、TLMを実行したりすることなどが可能です。

インストール後すぐにC/C++/SystemCの環境が利用できます。インストーラにはC/C++コンパイラと色々なCアプリケーション(SystemC, SystemC+SCV, PLI, VHPI)に必要なヘッダ・ファイルとライブラリ・ファイルが含まれています。C言語アプリケーションをコンパイルする場合は、専用のコマンドを使うことで、必要な定義、リンクしなければならないヘッダ・ファイルやライブラリ・ファイルのパスなどが自動で設定されます。そのため、設計者はC++コンパイラの警告に煩わされることなく、開発に専念することができます。アルデックのソリューションは強力なデバッギング・ツールも持っています。

アルデックのシミュレータはSystemC Verification Library(SCV)アプリケーションの開発とシミュレーションの環境もサポートしています。最近知名度の上がっているSCVはSystemCとTestbuilderをベースとして構築され、ランダム化技術、トランザクションの記録などの先進的な機能をサポートしています。ヘッダ・ファイルとコンパイル済みライブラリ・ファイルがアルデックの製品に添付されています。

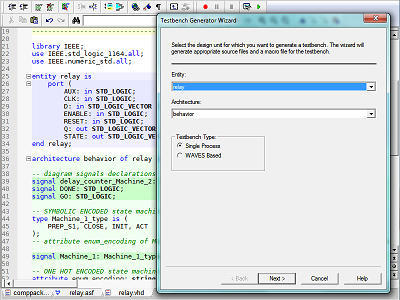

テストベンチ生成

テストベンチ生成ツールは、ユーザ定義の仕様に基づいてテストベンチ・ファイルを自動生成するツールです。空のテストベンチのシェル(スティミュラスなし)を生成したり、スティミュラス付きの完全なテストベンチを生成したりできます。スティミュラス付きのテストベンチを作るにはテスト・ベクタ・ファイルが必要です。テストベンチはそのファイルで定義されたテスト・ベクタを基にしてUUTエンティティのスティミュラスを生成します。また、波形エディタで作成するか、シミュレーション実行中に作成された波形からデザイン・ユニットのテストベンチを生成することもできます。

テストベンチ生成ツールのメリット

- 機能検証をスピードアップできる強力なテストベンチ生成ツール

- 生成したテストベンチは自由に編集可能

- ステート・マシン用テストベンチの自動生成では、ステート・マシンの中をすべてをテストできるテストベンチを生成可能

- アルデックのツールに付属のSystemC Verification Library(SCV)で制約付きスティミュラスとランダム・スティミュラスを作成可能。SCVとトランザクタ・メソドロジを組み合わせれば、スティミュラスも自動生成する高機能テストベンチを作れる強力なツールが完成

- MATLAB/Simulinkとのインタフェースで、複雑な数式を持つ高機能テストベンチから、テストユニット(UUT)にスティミュラスを与えることが可能

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.