非同期クロックドメイン検証

CDCおよびRDC検証ソリューション

ALINT-PRO™には、最新のマルチクロックおよびマルチリセットデザインにおけるクロックとリセットのドメインクロッシング解析に加え、複雑なメタスタビリティ問題の処理に焦点を当てたALDEC_CDCルールプラグインがあります。RTLデザインおよび機能検証段階で重要な問題を明らかにするルールが含まれ、市場投入めでの時間を大幅に短縮します。

クロックドメインクロッシング(CDC)の問題は、アプリケーションの種類や実装テクノロジに関係なく、昨今のデザインの大多数において複雑かつ広く普及している検証問題です。独立した相互作用するクロック数と、それに関連する設計上のミスは、ほとんどの業界で継続的に増加しています。

リセットドメインクロッシング(RDC)問題は、比較的新しいクラスのエラーになります。これは動的に切り替え可能な機能を持つ複雑なリセットストラテジを使用したデザインに一般的であり、デザインの特定の領域内でより頻繁なリセットシーケンスが必要になります。

経験則として、RDC関連のメタスタビリティはリセットイベント中にのみ発生し、CDC関連のメタスタビリティはいつでも発生する可能性があるため、CDCバグはRDCバグよりも高い確率を持っています。それでもドメインクロッシングの問題を両クラスでクリーンアップすることは非常に重要であり、両タイプの問題の検証方法には多くの共通点があります。

ALINT-PROには、メタスタビリティ問題の解析を容易にするために設計されたCDCおよびRDCビューアが搭載されています。RTL Schematic Viewerで非同期クロックまたはリセットドメインを異なる色で視覚化したり、検出されたクロックとリセットドメイン要素の詳細表示、関連するクロックおよびリセット信号、グループで識別されたドメインクロッシング、シンクロナイザが検出された非同期転送が適切に処理されているかどうかを理解できるようにします。これにより、クロックおよびリセットドメインのパーティションに関する高レベルのデザイン解析が可能になります。

デザイン制約のサポート

デザイン制約のサポートは精確なクロックドメイン検証に不可欠な機能のひとつです。ALINT-PROはデザイン設定用のSDCファイルを読み込んでリントに関連する情報を取り出します。これには、クロック宣言とそれらの関係性や、入力・出力ポートとクロックとの相互関係、非同期および物理的/論理的に排他的なクロックグループ、falseおよびマルチサイクルパス、ケース解析のセットアップなどが含まれます。

ALINT-PROは、制約がない場合でもネットリストトポロジと事前定義された回路パターンに基づいてクロックの構造の検出、リセットネットワーク、I/O遅延、クロックグループ、およびシンクロナイザ回路を自動的に検出しようとします。このツールはSDCファイルの初期ドラフトを生成して、タイミングドリブンの論理合成やスタティックタイミング解析などの設計の後工程で使用できます。生成されたSDCドラフトには、マスタおよび生成クロックを含むクロック宣言、非同期クロックグループ、およびトップレベルポートに対応する読取り/書込みクロックを使用したI/O遅延の記述が含まれています。正確なクロック周波数と遅延値はRTLから抽出できないため、デフォルト値が使用されます。そのため、後工程の設計ツールで使用する前に調整する必要があります。構造検証の結果に基づいて、ALINT-PROはタイミング例外を宣言し、ベンダー固有の配置配線およびスタティックタイミング解析ツールによる消費のための追加の情報を提供する、最も難しいSDC制約のテンプレートを生成することもできます。

部分的に指定されたSDC入力と自動検出の混在は許されています。どちらの方法も互いに補完し合うため、SDCを使用して自動検出を正しい方向に向けることができますが、高度なケース、特に複雑なカスタムクロックゲーティングを持つASICデザイン、多重化およびスキャン回路ではこれを回避するのが困難な場合があります。

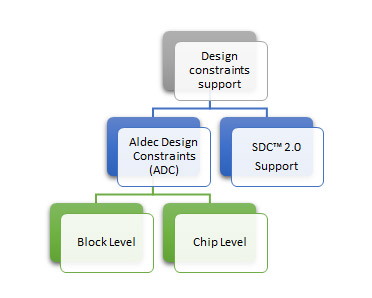

ALINT-PROは、デザイン制約のカスタム拡張機能であるAldec Design Constraints(ADC)を提供します。これらの拡張機能は、リセットセマンティクスなどの一般にサポートされているSDC構文では表現できないデザインの要素に関する高レベルの意図をキャプチャするのに役立ちます。したがって、ADCは広範囲におよぶSDCのスーパーセットと考えることができます。純粋なトポロジに基づいたマスターリセットや生成されたリセットなどのADC拡張機能の生成は、SDC処理フローと同様に提供されます。

これらの拡張ADC制約は、2つのグループに分けられます:

- ブロックレベル・デザイン制約 - FPGAベンダ・プリミティブ、ビヘビアモデル、暗号化IPなどの直接合成ができないモジュールの記述に使用します。カスタムシンクロナイザ、クロックおよびリセット生成セル、特定のRAMおよびFIFOを記述して、これらがデザイン内で正しく使われているかどうか検証することもできます。

- チップレベル・デザイン制約 - リセット・ネットワーク、quasi-staticレジスタ、CDCおよびRDCの除外の記述、およびネットリストからの追加情報の取得に使用されます。

ALINT-PROは、最も関連性の高いXilinx、Intel(Altera)、Microsemi、およびLattice FPGAライブラリに対して、クロックピンに関連する入出力遅延、および特定のジェネリック値に依存するタイミング動作を持つマルチモードプリミティブを含む、事前にパッケージ化された最新の正確なタイミングアノテーション(ブロックレベル制約)を提供します。これにより、CDC/ DCの誤検出の量が劇的に減少し、以前は見えなかったクロックとリセットドメインのクロッシングパスが明らかになります。

複雑なマルチクロックIPブロック(暗号化されたコアなど)およびその他のタイプのブラックボックスをインスタンスするデザインには、カスタムブロックレベルの制約を記述する必要があります。クロックと非同期制御ピンを明示的に宣言し、非制御I/Oピンと想定クロックとの関係を表現する必要があります。ブラックボックスに関連付けられた明確なタイミングの抽象がないと、ALINT-PROはブロック内のクロックドメインクロッシングについて悲観的な仮定を行い、多くの誤検出メッセージを生成する可能性があります。ブロックレベルデザイン制約は、階層的なアプローチを使用してCDC解析のパフォーマンスを改善するためにも使用できます。大きなデザインブロックが内部のCDC問題に対して既に検証されている場合、検証されたブロックに関連する新しいCDC違反はそのI/O境界でのみ発生する可能性があるため、ブラックボックスおよびブロックレベルのデザイン制約モデルへの置き換えるは理にかなっています。

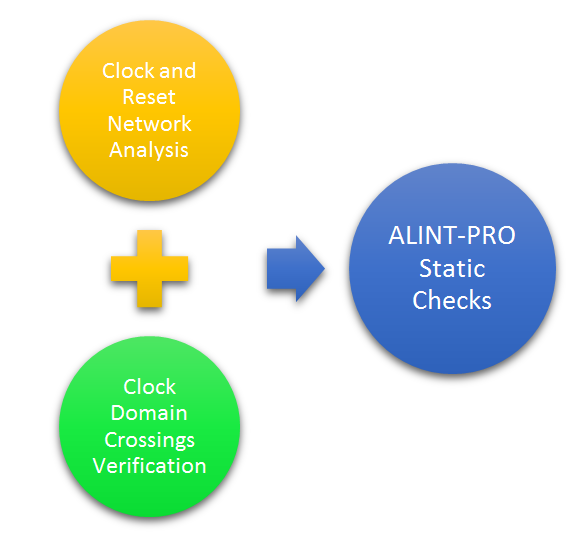

スタティック検証

クロックおよびリセットネットワーク検証はCDCチェック前に実行され、適切なクロックドメインの抽出を確認します。

CDCルールは非同期クロックドメイン間のクロッシングを検証します。データ転送については、組み合わせ回路があるかどうかや、コンバージェンス、ディバージェンスなどについて検証します。転送際に妥当なシンクロナイザがあるかどうかもチェックします。非同期リセットについては、アサーション停止が適切なクロックと同期しているかどうかがチェックされます。クロッシングは、組合せロジック、収束または分岐があるかどうかを検証します。有効なシンクロナイザーがクロッシングポイントに存在することも確認されます。 非同期リセットの場合、デアサートが適切なクロックと同期していることが検証されます。最後にカバーされていないシンクロナイザは、ターゲットドメインの非常に深い場所にある組合せまたはシーケンシャルのリコンバージェンスに対してチェックします。

RDCルールは、独立したリセットドメイン間クロッシングを検証し、RDC固有の同期パターンを探します。異なるドメインからのリセットはペアで解析されます。同じクロッシングに対しても複数の異なるリセット信号の組み合わせによりパスが非同期となり、メタスタビリティ状態が発生する可能性があります。

スタティックまたはダイナミックに選択できる複数のクロック動作モードを使用したデザインを解析する際には、特別な注意が必要となり、CDC検証が大幅に複雑になります。ALINT-PROは、統合されたマルチモード方式、または個別ケースごとのモーダルCDC解析をサポートできます。

統合されたマルチモードCDC解析の主な差別化要因は、ツールを実行するだけですべての有効なモードで予期しないすべてのCDCトポロジを一度にリストする結合検証結果を生成することです。無効なアクティベーション条件はスマートに除去されるため、関連するモードの組み合わせのみがチェックされます。有効なモードの数が多いと、CDCチェックの結果の解釈が間違いなく複雑になります。ただし、パフォーマンスは大幅に節約されます。

あるいは、各動作モードのそれぞれのモードに対応する"set_case_analysis"制約を使用して個別に解析することもできます。これにより、解析中に非アクティブなパスが基本的に排除されます。このタイプの検証結果は理解することがはるかに簡単ですが、各モードごとに複数回実行する必要があり、デザイン自体または関連するタイミング制約に修正が発生した場合、検証を最初からすべてのモードで再実行する必要があります。

ダイナミック検証

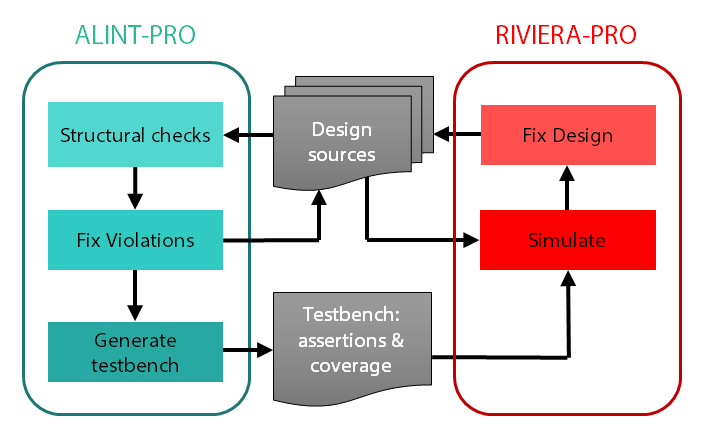

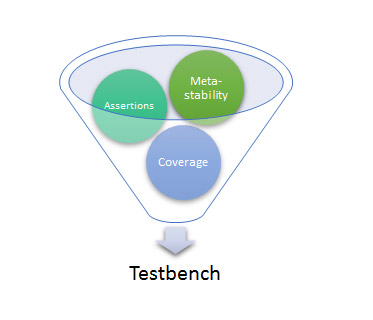

構造検証は非同期間転送時に適切なシンクロナイザがあるかどうかチェックできますが、CDCのバグがないことを保証するには、通信プロトコルを検証する必要があります。ALINT-PROはSystemVerilog、VHDLのみ、およびVHDLとPSLのテストベンチを生成して、RTLシミュレーションを拡張してチェック項目を増やすことができます。テストベンチは次の要素で構成されます:

- メタステーブルのエミュレーション – SystemVerilogまたはVHDLの動作コードは、非同期クロックドメイン間のデータ転送ポイントにランダム遅延を挿入します。それによってRTLシミュレーション中にパルス失敗やデータ不整合などを発見できるようになります

- アサーション – アサーションは非同期転送時の同期を取ることでシンクロナイザが正しく使われているかどうかを確認するためのものです。チェック項目としては、データの安定性や、クロックドメイン境界をまたいで送信されるデータが正しくキャプチャされているかどうか、などです。

- カバレッジ – ユーザーのテストベンチが同期転送時にデータ転送をトリガするかどうか、またメタ・ステーブルのエミュレーションとして挿入されたランダム遅延がシミュレーション中に実際に発生するかどうかをチェックすることができます。

ここで生成されるテストベンチにはスティミュラスがないので、シミュレーションに利用するにはデザインの元々のテストベンチが必要です。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.