ハードウェア・エミュレーション・ソリューション

|

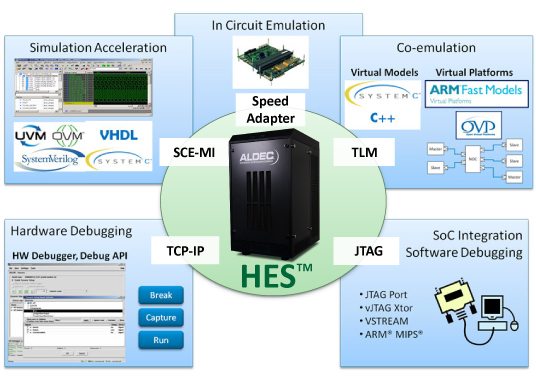

HES-DVM™は最新のSoCやASICを設計するハードウェアチームとソフトウェアチーム向けのハイブリッド検証・バリデーション・システムです。最新の大容量FPGAテクノロジと業界最先端の協調エミュレーション規格を組み合わせることで、HES-DVMは次のような複数の検証モードをユーザーに提供します。

アルデックは次の5要素をひとつにしてHES™を構成し、業界最高クラスのハードウェア・エミュレーション・ソリューションを実現しました。

検証用IP エミュレーション・システムは検証用ファームIP(VIP)を揃えたライブラリがなければ完成しません。AMBA AHB, AXIなどの業界標準のバス・プロトコルやUSB, PCIe, Ethernetなどの通信ペリフェラルについて、トランザクタ、ドライバ、モニタ、スピードアダプタを用意することが、信頼できるデザイン検証環境を素早く構築してエミュレーションを成功させるための鍵です。アルデックが用意するVIPは、検証後テープアウトに成功したSoCデザインで検証されており、変更なしですぐに応用できます。それ以外のVIPについても、アルデックの専門チームが開発体制を整えて、ユーザの検証用IP準備を援護します。

デバッギング・ツール HES™はデザインを完全に可視化するトゥルーRTLビューや、メモリビュー・変更、トリガ、ブレークポイント、クロック・ステップ制御など、色々なデバッグ機能を搭載しています。トゥルーRTLビューとは、すべてのデバッグ・プローブが保存され、元の信号の名前とデータタイプと階層が維持されるという意味です。ASDBやFSDBなど色々な波形フォーマットを選べるので、アルデックのツールやサードパーティのツールとの統合も可能です。デバッグ機能はすべて、ハードウェア・デバッグツールの内部で、また専用のHES Debug APIを介してテストベンチで利用可能で、どちらもTCP/IP経由の遠隔アクセスに対応しています。 |

関連するアプリケーション

協調エミュレーションUVMシミュレーション・アクセラレーションアクセラレーションのスケーラビリティ検証用IPSoCのパーティショニングエミュレーション・デバッギング 関連するプロダクト |

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.