SoCのパーティショニング

今日、システム・オンチップ(SoC)はエンターテインメントからウェアラブル・エレクトロニクス、医療、自動車、さらには航空宇宙分野など幅広い用途に使われています。Internet of Things(IoT)の時代が近付く中、近い将来SoCのアプリケーションは間違いなくさらに拡大すると思われます。

このような状況で、検証エンジニアには非常に大きな要求がのしかかり、高品質なSoCを期限までに確実に検証しテープアウトできるように、能率的な手法が必要とされています。このような理由で、FPGAプロトタイピングとエミュレータが普及するようになりました。SoCは規模が大きいため、プロトタイピング・ボードは大規模FPGAデバイスを複数搭載し、また簡単に拡張できなければなりません。目的に合ったFPGAプロトタイピング・ボードを選択または開発し、デザインのパーティショニングを適切に行うことは、多くのチームにとっては難問です。

SoCデザインのアーキテクチャ

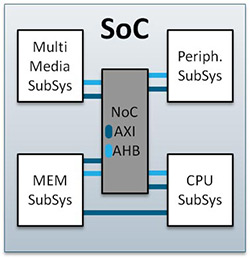

ASICデザインの観点から考えると、SoCは単一機能専用のデザインから複雑なマルチファンクション・システムへのパラダイム・シフトです。このトレンドに遅れずについて行くために、SoCプロジェクトは再利用可能なIPコアやAXI, AHB, Wishbone, OCPなどの標準バスなどからなるアーキテクチャを必要としています。これらはさらに統合されてネットワーク・オンチップ(NoC)を構成します。

ASICデザインの観点から考えると、SoCは単一機能専用のデザインから複雑なマルチファンクション・システムへのパラダイム・シフトです。このトレンドに遅れずについて行くために、SoCプロジェクトは再利用可能なIPコアやAXI, AHB, Wishbone, OCPなどの標準バスなどからなるアーキテクチャを必要としています。これらはさらに統合されてネットワーク・オンチップ(NoC)を構成します。

こうしたモジュール式のデザインや、標準バスを応用することで、シミュレーションだけでなくエミュレーションやプロトタイピングでもサブシステムを個別に検証することが可能になりました。その後、SoCプロトタイピングのインテグレーションについては、サブシステムがデザイン・パーティショニングの基本構造単位にもなります。

スケーラブルなFPGAプロトタイピング・ボード

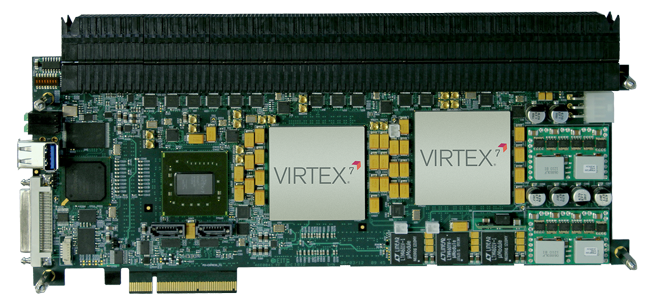

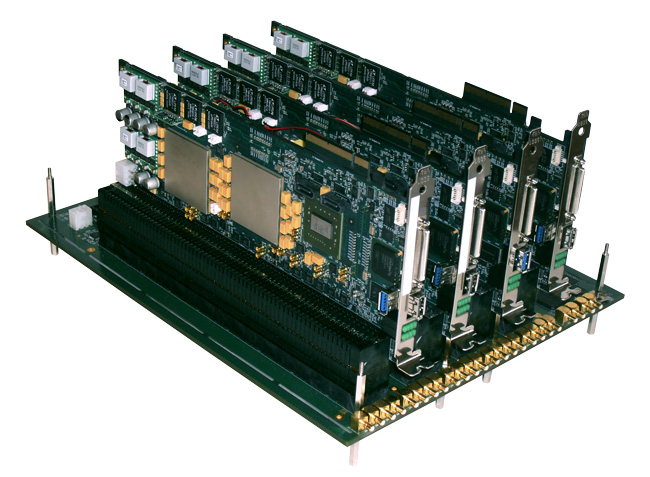

モジュール式のSoCデザインには、柔軟でスケーラブルなプロトタイピング・ソリューションが必要です。スケーラビリティは、 HES-7などのバックブレーンとベースボードで構成され、プロトタイプの実装やフレキシブルな拡張が可能なモジュール式設計で実現できます。HES-7はオープン仕様のバックプレーン・コネクタでプロトタイプ容量を最大2億8800万ASICゲートまで簡単に拡張できます。HES-7シリーズには2種類のベースボードがあります。

| HES-7プロトタイピング・ベースボード | |

|---|---|

| HES7VX4000BP | HES7VX12000BP |

| Virtex 7 2000 FPGA 2個搭載(最大2400万ゲート) | Virtex 7 2000 FPGA 6個搭載(最大7200万ゲート) |

|

|

HES-7プラットフォームがスケーラブルなのは、ベースボード単独でもPCIeホストコネクタがあり、全ての機能のプロトタイピング・ベンチとして使えるからです。ボード1枚の構成は小規模なSoCや部分的なサブシステムの検証に最適です。デザインが大規模化した場合、またはサブシステムを含めてSoC全体を検証する段階になったら、バックプレーンで拡張できます。

高集積FPGAを搭載したプロトタイピング・ボードのバックブレーンを堅牢に造るのは、開発とテストに何ヶ月もかかる面倒な作業です。最大伝送速度を出すためには、バックプレーンのトレースをよく考えて配線しなければなりません。バックプレーンのインターコネクトはFPGA間転送にボトルネックが発生してプロトタイプ全体の速度に影響が出ないように、うまくバランスを取る必要があります。

高集積FPGAを搭載したプロトタイピング・ボードのバックブレーンを堅牢に造るのは、開発とテストに何ヶ月もかかる面倒な作業です。最大伝送速度を出すためには、バックプレーンのトレースをよく考えて配線しなければなりません。バックプレーンのインターコネクトはFPGA間転送にボトルネックが発生してプロトタイプ全体の速度に影響が出ないように、うまくバランスを取る必要があります。

インターコネクトのバランスの例として、HES7BPX4のバックプレーン・ボードを考えます。下のブロック図は、ベースボードHES7VX4000BPを4スロットすべてに接続した場合の8個のFPGAのインターコネクトを表しています。

このボード構成では、たいていのSoCデザインで最適な接続を確実に作れます。他の手法としては、ボードのレイアウトをSoCのサブシステムの接続に一致させる方法もありますが、ボードを1プロジェクトでしか使えないため一般的ではありません。

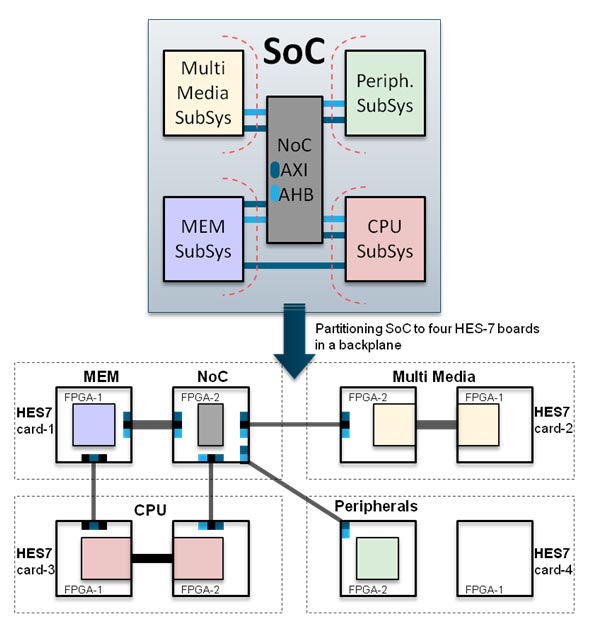

SoCの階層的パーティショニング

SoCのアーキテクチャは、サブシステムごとにデザインを分ければパーティション同士の境界が自然と見えて来るようになっています。また、サブシステムは普通、それぞれ違うクロック比で実行されます。この性質を考えると、ローカル生成のクロックでサブシステムを駆動することで、プロトタイプとエミュレーションのスピードをできるだけ高めることができます。こうしたことをすべて織り込んで、SoCは次の図のようにHES7BPX4にマッピングできます。

HES-7を導入したデザインのメリット

- 最大2億8800万ASICゲートのスケーラブルな容量

- ボード1枚に最多で6個のFPGA, バックプレーン構成で最多24個まで搭載可能

- オープン仕様のドーターカード・コネクタで外部ペリフェラルとインタフェースを接続可能

- ドーターカード経由でペリフェラルとインタフェースをサポート、Xilinx® Zynq™上のARM® Cortex™など

- サブシステムのプロトタイピングとSoC全体のインテグレーションが可能

- プロトタイピング・ハードウェアの再利用による高速化とエミュレーション検証モード

- 高速USBベースのユーティリティでFPGAプログラミングとボード設定

- ラックマウント式のシャシーでバックプレーン構成

- 最高品質をバックアップする業界随一の1年間保証

- 検証とFPGAプロトタイピングの分野で30年以上の経験を持つ実績あるメーカー

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.