高頻度トレーディング

高頻度トレーディング(HFT)では、FPGAの人気と評価がこの5年間に大きく伸びました。その最大の理由はレイテンシです。HFTに取り組む会社は限りなくゼロに近いレイテンシを目指し、競争に勝ち残るために最新技術を採り入れなければなりません。いちばん高速なシステムを持つ者が生き残ります。

FPGAは何百万もの論理ゲートを持ち、データを順次処理していくソフトウェアとは違い、データを並列に処理することができます。そのため、レイテンシが数千分の1秒というソフトウェアに比べて、FPGAは数万分の1秒のレイテンシを達成しています。FPGAは数値演算を並列処理できるDSPブロックを数千個持っていて、しかも再プログラミング可能で現場でも最適化可能なフレキシブルなシステムが作れます。

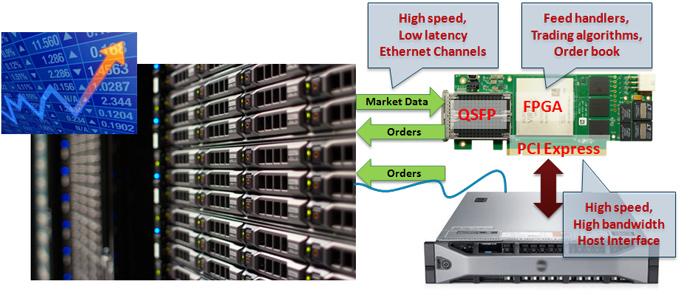

FPGA/ASICプロトタイピングとアクセラレーションに30年以上の経験があるアルデックの提供するFPGAアクセラレータは、PCIe/QSFPインタフェースを搭載し、1U(またはそれ以上の)取引システムと互換性があり、かつマーケットメイキング、統計的アービトラージ、アルゴリズム取引など時間がカギを握る取引戦略に向いています。

低レイテンシの達成

絶対要件である低レイテンシは最新世代の Xilinx FPGA – Virtex™ UltraScale+ を搭載して、Ethernet/QSFPやPCI Expressなどの必須インタフェースをFPGAに直に接続することで達成しました。ネットワークインタフェース(QSFP)から直接取り込んだ市場データのフィードはすぐさま内部のFPGAファブリックで処理されます。FPGAファブリックには特定タスクに特化した並列プロセッサが何百個も並んでいます。2番目のQSFPリンクはFPGA内部で実行されるアルゴリズムからの結果を受けて、売買の注文やキャンセルを出します。また、事前に処理されたデータをPCIeインタフェースを経由してホストのワークステーションに送信して既存のソフトウェアで分析することもできます。FPGAのパイプライン機能でインタフェースを並列に動かすこともできます。

臨機応変に再構成が可能

FPGAはシステム全体をシャットダウンせずに臨機応変に再構成が可能なので、設定の柔軟性が大きく上がり、ダイナミックに動く取引環境に素早く対応することが可能です。新しいFPGAアクセラレータは1U以上の取引システムと互換性があり、時間が重要な取引戦略に向いています。

FPGAデザインの開発とデバッグ

すべて揃ったFPGA開発環境が必要なお客様は、当社にお問い合わせいただければ、FPGAアクセラレータボードとRTL開発・シミュレーションツールをまとめてご提供します。このセットには、Riviera-PROのような高性能・混合言語(VHDL/Verilog/SystemVerilog/SystemC)シミュレータ、PythonによるFPGAテストベンチのサポートなどが含まれます。

IPパートナーのIPコア(市場データフィードハンドラなどの取引システムの機能ブロック)を統合します。

主な機能

- 最新のXilinx UltraScale+ FPGAで高速処理

- スピードグレード(-2)の高いFPGAを使用

- 低レイテンシのインタフェースQSFP28

- 高帯域ホストインタフェースPCI Express 16x gen3

- 高速なQDR-IIメモリ

- ロープロファイルボード(1Uラックサーバにマウント可能)

- 実行中の再構成が可能(電源を落とさず、PCIeリンクがアクティブでもFPGAを再構成可能)

- FPGAのデザインのノウハウを持つソリューションベンダ

ソリューション内容

- FPGAボード、ロープロファイル、PCIe、低レイテンシインタフェース、1Uラックサーバのサポート

- 高性能シミュレータRiviera-PROでHDLでのアルゴリズム開発サポート

- 低レイテンシのEthernetを実現するIPパートナー

- QSFPとPCIeのインタフェースとQDR-IIメモリコントローラを持つリファレンスデザインと診断用デザイン

- インテグレーションコンサルティング・サービス

パートナー開発環境

|

Tamba Networks

|

|

Northwest Logic

|

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.