マルチFPGAデザインのパーティショニング

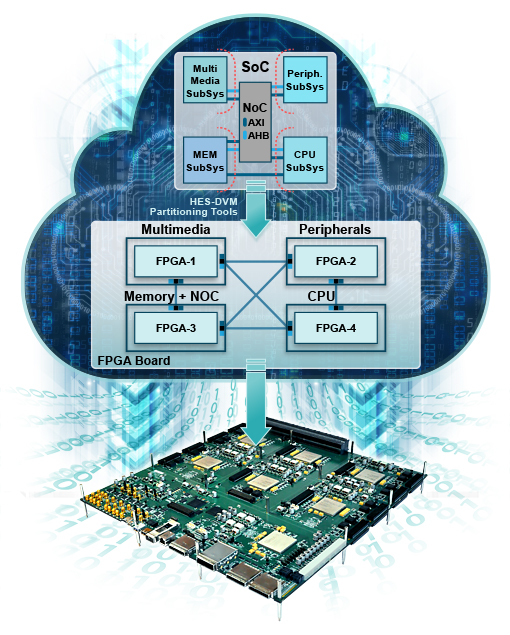

近年のSoCデザインは非常に大規模化が進み、プロトタイピングボードには大容量FPGAが複数必要であり、さらにスケーラビリティ(または拡張性)も必要になっています。最適なFPGAプロトタイピングボードとデザインパーティショニング方法を選ぶことは、多くの設計者の課題の1つになります。デザインを各FPGAに合う様にブロック分割が必要なだけでなく、それらの接続をボード上の物理I/Oとトレースで正確に接続する必要があります。たとえば、 HES™プロトタイピングプラットフォーム(バックプレーンを使用)で実装された6億3300万ASICゲートのデザインの物理接続は以下の様になります。

物理I/Oとトレースの数は常に不足気味で、増え続けるFPGAのサイズに追いついていません。高速シリアルI/OとLVDS伝送が可能なI/Oでこの制約を克服できますが、そうするとユーザーはFPGAプロトタイピングボード上のデザインパーティションを時分割多重(TDM)技術で接続する必要があります。さらにもう1つ問題になるのが、正しいクロックの分配とボードレベルでのタイミング精度の保証です。

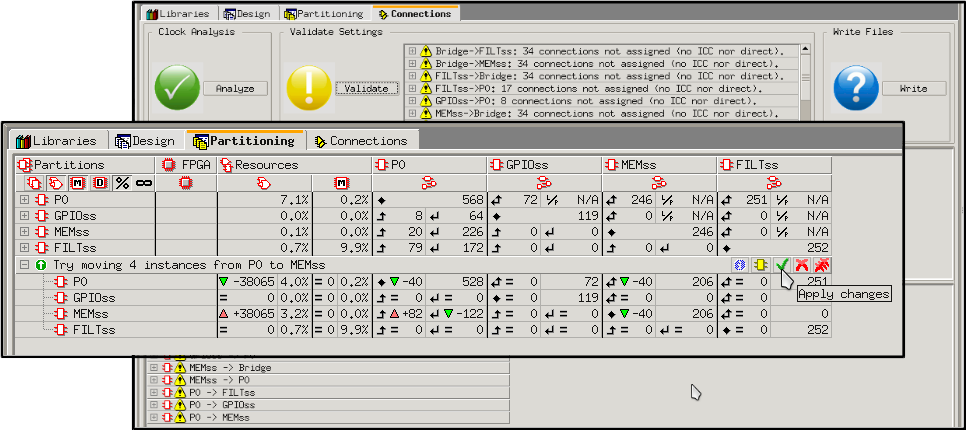

こうした課題は、すべてアルデック HES-DVMソフトウェアで解決できます。HES-DVMでは、プロトタイピングフローを管理できるほか、デザインパーティショニング、相互接続、クロックマッピング、およびタイミングクロージャが可能なツールを利用することができます。

HES-DVM Protoの主な機能と利点

- マルチFPGAでのプロトタイピングを素早くセットアップ

- デザイン構造モデルとトップダウン戦略でパーティショニングを支援

- 色々なパーティションにクロックを供給するためのインスタンスロジックレプリケーション

- 消費ロジックリソースとインターコネクトを監視

- ドライランと「what if」影響解析で色々なパーティションのパターンをシミュレーション

- ゲーテッドロジックの自動変換とネットリスト最適化

- クロックドメインクロッシングアナライザとタイミング制約エディタ

- アルデック HESボード、および他社カスタムボードなどをサポート

- ボードレベルでの接続リソース認識、グローバルクロックとトレース、LVDS、シングルエンド

- チップ間接続(ICC)バスの自動挿入

○ SERDESモジュール利用

○ LVDSまたはシングルエンド信号

○ 直接ルーティングまたはグローバルトレース

- 決定したパーティショニングを総合的に検証できるクイックチェックリスト生成

- パーティショニング後のシミュレーションのサポート

プロダクトビデオ(英語)

HES-DVM Proto CE - Getting Started |

|

|

このビデオでは、HES-DVMパーティショニングツールを使用して、FPGAデザインプロトタイピングに必要なファイルを準備する方法を学習します。 HES-DVM™は、SoCおよびASIC設計向けの完全に自動化されたスケーラブルなハイブリッド検証環境です。 |

|

Board Compiler - Defining Custom FPGA Board for Prototype Partitioning |

|

|

このビデオではアルデックのFarhad Fallahが、HES DVMボードコンパイラツールを使用して、プロトタイピング用にDVMで使用するカスタムボードファイルを準備する方法を説明します。 ボードコンパイラはLinuxコマンドラインツールであり、ユーザーはボードファイルを準備し、ツールへの入力として使用する必要があります。 |

|

Fully Automated Design Partitioning Guide |

|

|

このビデオではアルデックのFarhad Fallahが、HES DVMツールの自動マルチFPGAパーティショニング機能について詳しく説明しています。 AWSクラウドでHES DVMを使用して、ASICデザインをマルチFPGAに自動的に分割する方法を学習します。これには、検証エンジニアにとって多くの時間がかかります。 |

|

Deep Dive Into Design Partitioning |

|

|

ASIC/SoCデバイスのモジュール数の指数関数的な増加は、検証エンジニアにとって複雑な課題になっています。 大きなデザインをプロトタイピング用の単一のFPGAに収めることは不可能であるため、マルチFPGAパーティショニングの需要が高くなっています。 |

|

Connections Tab Deep Dive |

|

|

ASICおよびSoC設計で使用されるIOの数は、ムーアの法則とほぼ同じように増加しています。 FPGA上の物理IOの数に制限があるため、大量のIOを必要とするより複雑なSoC設計のプロトタイピングは非常に困難になっています。 |

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.