Active-HDL が提供する HDL デバッグ機能

概要

デザインの検証処理は一般的に、モデルの動作をよく理解していることはもちろんのこと、多くの面倒な作業を含んでいます。しかし VHDL と Verilog 言語はあらゆるモデルの記述がベンダ固有ではなく交換可能であることを保証するため、デザインの検証結果は長く持続する効果をもたらします。誰でもたまには間違いをするため、デザインのエラーチェックが必要となります。Active-HDL は、VHDL と Verilog コードのデバッグを行ういくつかのメカニズムを提供しています。

-

シンタックスチェック - コンパイルコマンド実行時にチェック

-

コードトレース - HDL コードを構文単位で実行、またはプロセス文やサブプログラム、プロシージャ毎にトレース

-

値の検証 - 変数値を Watch や List ウィンドウで表示

シンタックスチェック

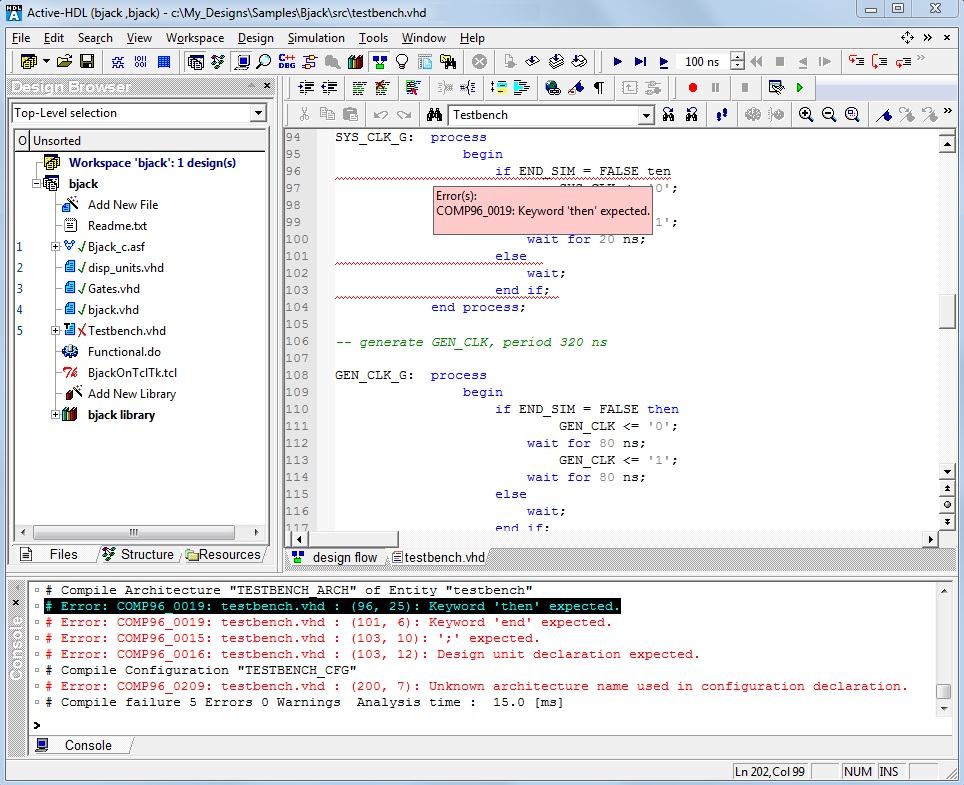

Active-HDL はインタラクティブな VHDL/Verilog コードデバッガを提供しています。コンパイルコマンド実行後には、コンソールウィンドウにコンパイル時に検出されたエラーが表示されます。各エラーは下記の付加情報も表示します。

-

ソースファイルの名前

-

エラー番号

-

ソースコードのエラー発生行とカラム番号

-

簡潔なエラー内容

エラーメッセージをダブルクリックすると HDL エディタが開き、コードのエラー発生行が表示されます。エラー行には赤い下線が引かれ、赤い×印が左に付いています。エラー行の上にカーソルを合わせると、コンソールウィンドウに通知されるのと同じエラーメッセージが表示されます。

インタラクティブなデバッグ

コンパイルコマンドは、HDL ソースコードが VHDL/Verilog LRM に準拠しているかを自動でチェックします。

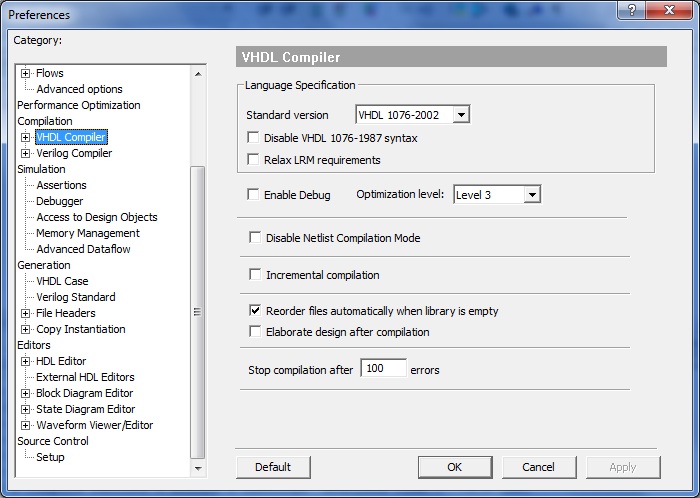

VHDL のデフォルトでは、100個のシンタックスエラーを検出すると、コンパイラは処理を停止しますが、Preferences にてデフォルト値を変更することができます。

注意: Tools | Preferences Compilation の Stop compilation after 100 errors にて設定します。

VHDL コンパイラの設定

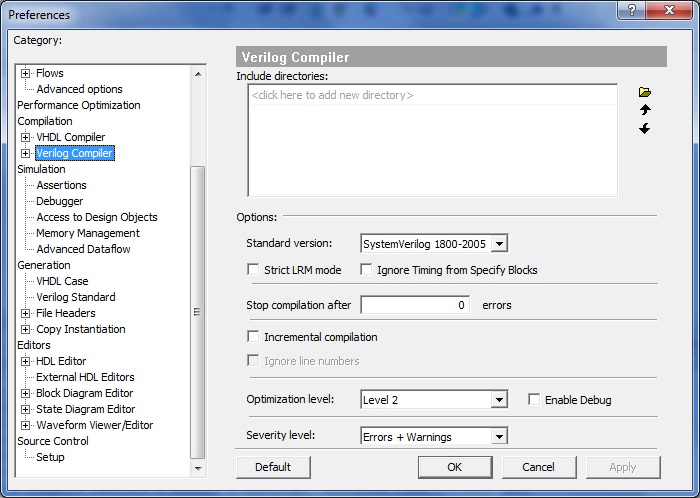

Verilog コンパイラの設定

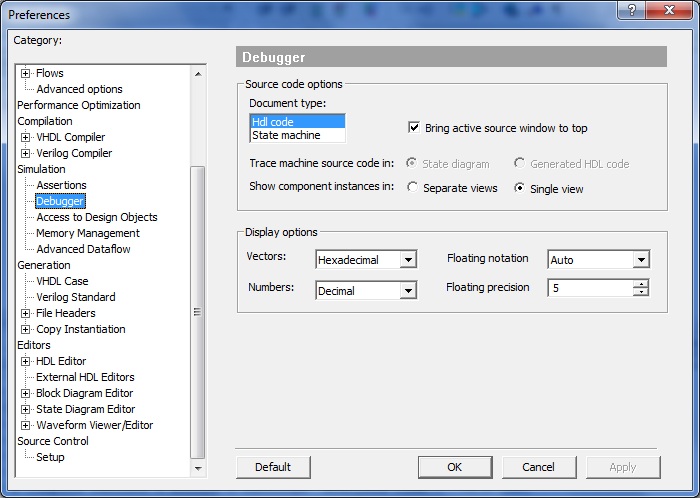

Preferences では、デバッグオプションのカスタマイズも可能です。Simulation Debugger にて、コードトレースの設定を変更できます。ドキュメントタイプとして、HDL コードとステートマシンが選択できます。Bring active source window チェックボックスにチェックを入れると、現在デバッグ中のソースコードがHDLエディタに表示されます。Show component instances in では、各コンポーネントの表示方法を指定でき、コンポーネント毎の表示か単一表示かを選択できます。

Preferences | Simulation Debugger の設定

Active-HDL では、ステートマシンから生成された HDL コードについてエラーをチェックすることが可能です。上記ウィンドウにて、次のどちらかのオプションを選択できます。

-

ステートマシンをトレース

-

ステートマシンから生成された HDL コードをトレース

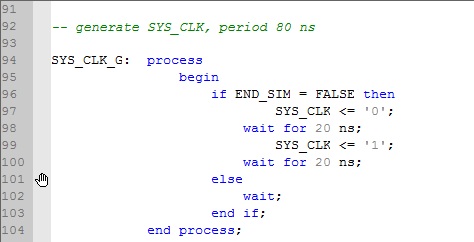

コードのトレース

ソースコードにシンタックスエラーがない場合、モデル動作の検証を開始できます。Active-HDL は全シミュレーション結果を表示する波形ウィンドウを提供します。ユーザは設計の間違いや期待と異なるレスポンスを素早く見つけることができます。

波形ウィンドウ機能の詳細は、波形ウィンドウアプリケーションノートを参照してください。

Active-HDL は、デザインの開発と検証用のインタラクティブなグラフィカル環境を提供します。必要に応じて、HDL ソースコードを構文単位でトレースすることができます。次の4つのコマンドがあります。

-

Trace into - 1つの HDL 構文を実行します。サブプログラムが呼び出されると、サブプログラムのボディに実行が移ります。

Trace into - 1つの HDL 構文を実行します。サブプログラムが呼び出されると、サブプログラムのボディに実行が移ります。 -

Trace over - 1つのVHDL または Verilog コマンドを実行します。サブプログラムが呼び出されると、サブプログラムのボディの構文がシングルステップで

Trace over - 1つのVHDL または Verilog コマンドを実行します。サブプログラムが呼び出されると、サブプログラムのボディの構文がシングルステップで

実行されます。 -

Trace out - 要求されるだけ多くの HDL 構文を実行し、サブプログラムの実行を終了します。サブプログラムが入れ子になっている場合、本コマンドにより

Trace out - 要求されるだけ多くの HDL 構文を実行し、サブプログラムの実行を終了します。サブプログラムが入れ子になっている場合、本コマンドにより

最内部のサブプログラムのみの実行を終了します。 -

Trace over transition -要求されるだけ多くの HDL 構文を実行し、ステート間のトランジションを実行します。

Trace over transition -要求されるだけ多くの HDL 構文を実行し、ステート間のトランジションを実行します。

これらのコマンドのどれかを実行するには、Simulation メニューから選択するか、トレースアイコンをクリックします。Trace over transition は、ステートマシンの

シミュレーション時のみ使用可能です。

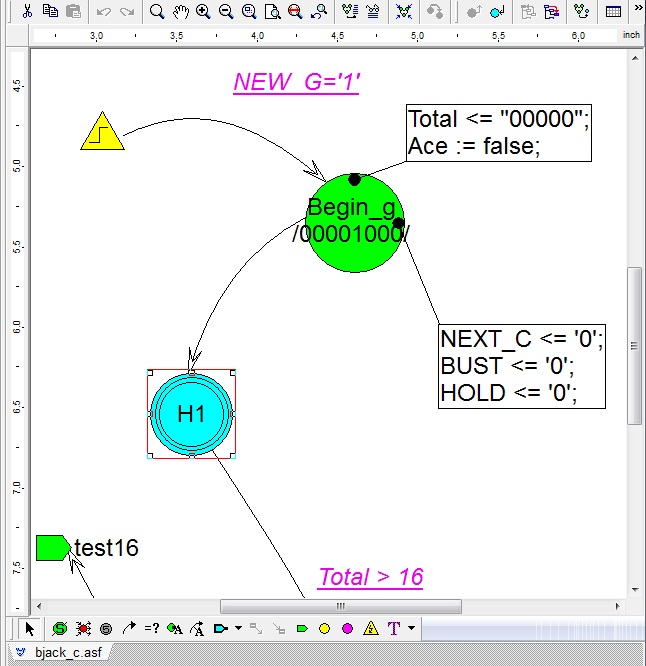

ステートマシンのソースコードデバッグ

Simulation メニューの Trace over Transition がステートマシンで利用できます。Active-HDL は、ステートマシンの入力と修正用のグラフィカルエディタを提供します。

さらにリアルタイムステートマシンエディタにより、ステートマシンの動作をインタラクティブにトレースでき、カレントステートは黄色で表示されるので視覚的に確認できます。

全てのトレースコマンドがデザインのデバッグ中に利用できるため、HDL コードの構文をトレースし、モデルの動作への影響を観測することができます。

ステートマシンエディタ

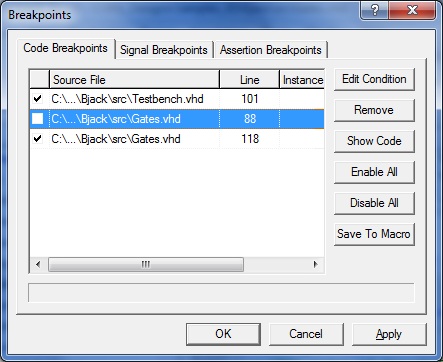

ブレークポイント

Active-HDL では、HDL コードにブレークポイントを設定することができます。ブレークポイントは、必要条件が発生するとシミュレーションを停止します。全ての処理を一時停止し、Watchウィンドウに信号値を表示します。HDL エディタでは、適切な行にだけブレークポイントが設定できます。例えば代入式を含む構文など。

シミュレーションブレークポイント

ブレークポイントエディタの Code Breakpoints タブには、コードブレークポイント設定用の3つのカラムがあります。

最初のカラムはブレークポイントを有効にするチェックボックスで、 2番目は ブレークポイントを設定するソースファイルのパス、3番目はそのソースコードの行番号です。

ブレークポイントエディタでは、ブレークポイントを手動で切り替えることができます。

Signal Breakpoints タブでは、トレースしたい信号を追加できます。信号名とシミュレーションを停止する条件、および信号値を表示する3つのカラムがあります。

Condition カラムでは下記の3つから選択可能です。

-

Event - 信号のイベント発生時にシミュレーションが停止します。

-

Value -信号が指定した値になった、または強制的のその値が与えられた場合、シミュレーションが停止します。

-

Transaction - 信号の遷移が発生した場合に、シミュレーションが停止します。

Code Breakpoints と Signal Breakpoints タブの Show Code ボタンをクリックすると、ブレークポイント設定行に即座にジャンプします。

複数のファイルを含むプロジェクトのシミュレション時には、これは大変便利な機能です。

コードブレ-クポイント

結果の確認

HDL コードのトレース時に、デザイン全体のレスポンスを確認することができます。さらにモデルには、テストを実行すべき特定条件があり、それらによりモデルの特定動作が発生しています。特定の信号値を観測するには、波形ウィンドウだけではなく下記のウィンドウに表示するのが最適であることがあります。

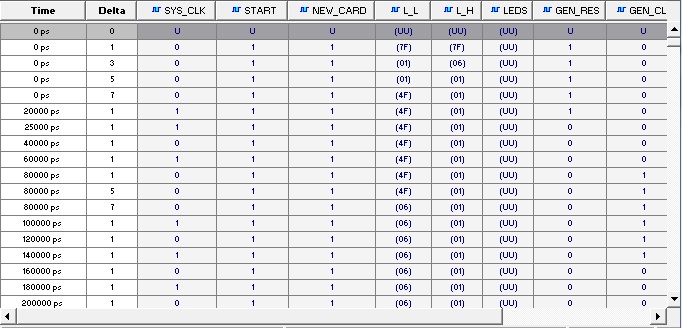

リストウィンドウ

リストウィンドウでは、全ての結果を表形式で表示します。リストウィンドウはシミュレーション結果の表示にのみ使用します。そのためスティミュレータを定義することはできません。

ウィンドウの内容はテキストファイルに保存できます。各信号はイベント発生時間のカラムに応じて表示されます。ウィンドウは下記の2つの方法で信号値を表示します。

-

指定時間実行された全シミュレーションサイクル

-

指定時間内の最後のシミュレーションサイクルのみ

-

リストウィンドウ

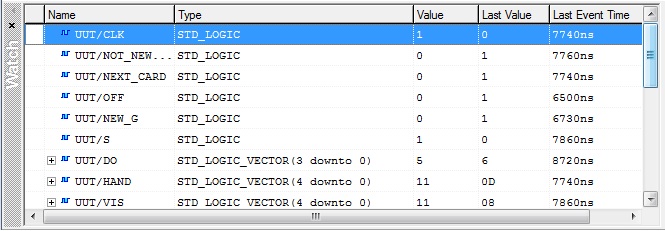

Watch ウィンドウ

最終値または現在の信号値を検査するには、Watch ウィンドウを使います。Watchウィンドウでは、選択した信号やポート、変数の値を表示します。

Watch ウィンドウ

ウィンドウは次の5つのカラムで構成されます。

-

名前

-

選択したオブジェクトのタイプ

-

現在の値

-

最終値

-

最終イベント発生時間

Watch ウィンドウに表示される全信号は、デザインブラウザからドラッグ&ドロップすることができます。HDL ソースコードから信号名をドラッグすることもできます。

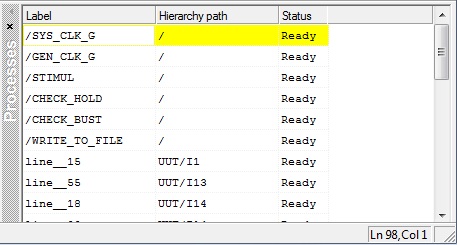

Processes ウィンドウ

Processes ウィンドウには、エラボレートされたモデルのプロセスリストを表示します。本ウィンドウはシミュレーション実行中のみ利用可能です。

Processes ウィンドウ

プロセスは、プロセスラベル、階層パスおよび各プロセスの状態を示す3つのカラムで表示されます。順序処理をモデリングしたコンカレント文が、ウィンドウに表示されます。

-

プロセス文

-

コンカレント信号代入文

-

コンカレントアサーション文

-

コンカレントプロシージャコール文

ラベルが付いていないプロセスには、プロセスが記述されているソースファイル行を示すデフォルトラベル (例: line__25) を、コンパイラが生成します。

generate 文で宣言されているプロセスの場合、ラベルはインスタンス数を示す添え字により修正されます。

Process ウィンドウに列挙されたプロセスは、 次の状態のどちらかになります。

-

Ready: 現在のシミュレーションサイクルでの実行が予定されているプロセスであることを示します。

-

Wait: 一時停止され、再実行を待っているプロセスであることを示します。

Processes ウィンドウには、次のどちらかを表示します。

-

現在のシミュレーションサイクルにおける状態に関わらず、エラボレートされたデザインにおいて選択された範囲すべてのプロセス

-

エラボレートされたデザインにおいて選択された範囲のアクティブなプロセスのみ、つまり現在のシミュレーションサイクルでの実行が予定されているプロセス

さらに、トレースしたいプロセスが記述されているデザインの範囲を選択することができます。

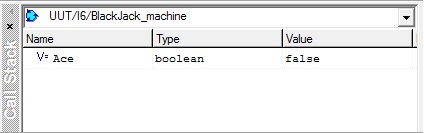

Call Stack ウィンドウ

Call Stack ウィンドウは、現在実行されているサブプログラム(プロシージャやファンクション)や変数のリストを表示するデバッグツールです。エラボレートされたモデルで

順序処理をモデリングしているコンカレント文を表示します。それらはプロセス文、コンカレント信号代入文、コンカレントアサーション文およびコンカレントプロシージャコール文です。 (Processes ウィンドウと全く同じです)。各サブプログラムについて、ウィンドウでは次の情報を表示します。

-

フォーマルパラメータと実際の値

-

サブプログラムのボディでローカルに宣言されている変数、定数およびファイルとそれらの現在の値

シミュレーションを実行したデザインに1つ以上のプロセスがある場合、Processes ウィンドウを使って、観測したいサブプログラムのプロセスを選択することができます。

Call Stack ウィンドウは、シミュレーション実行中のみ利用可能です。

Call Stack ウィンドウ

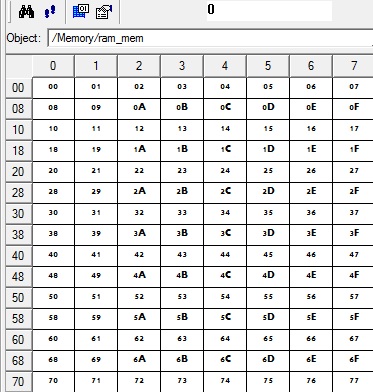

メモリビューワ

メモリビューワウィンドウは、アクティブなデザインで定義されているメモリの内容を表示するよう設計されているデバッグツールです。 (例:2次元配列タイプのオブジェクト)。

メモリに保存されている値、タイプ、ワード長、 メモリ深さおよびアドレスレンジがシミュレーション実行中に観測可能です。表示されるオブジェクトは、VHDL 信号と変数、またはレジスタや整数タイプの Verilog 配列のどちらかになります。

メモリビューワウィンドウでは、メモリセルのようなオブジェクトも表示可能です。ウィンドウではアドレスレンジの指定、メモリセルの値の編集、およびメモリ内容のテキストファイルへの保存が可能です。

メモリビューワウィンドウ

アドバンスドデータフロー

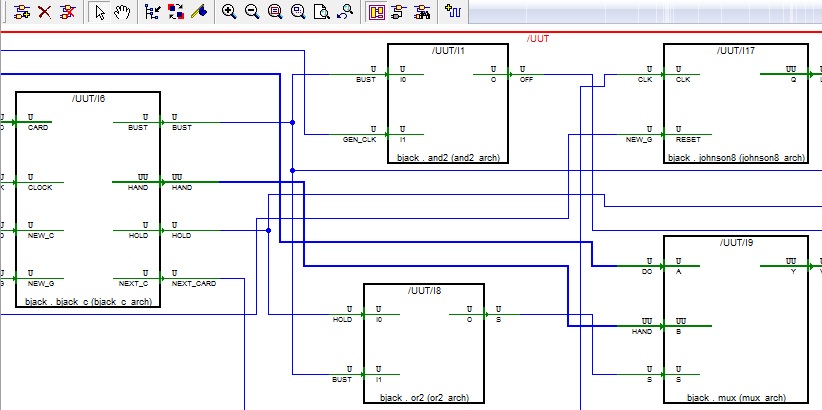

アドバンスドデータフローを使って、設計者はシミュレーション実行中にアクティブデザインの接続性を調査し、インスタンス、コンカレント文、信号、ネットおよびレジスタ間のデータフローを解析することができます。アドアンスドデータフロービューワにより表示される階層、フラットまたはグレーデータフローダイアグラムは、プロジェクト全体を通して伝搬するイベントのトレースや予期しない出力値の発生源を特定するのに特に有効です。

アドバンスドデータフローウィンドウ

Xトレース

X 値は、テストモジュールの予期しない出力値の発生源の可能性があります。 Active-HDL は、コマンドラインユーティリティとしてXトレースを提供しています。これによりユーザは、X や U 値が出力ポートに伝搬する前に、最初の発生時に検出することができます。Xトレースコマンドを-holdスイッチと一緒に使用すると、観測信号にX や U 値が割り当てられるとシミュレーションを停止します。予期しない値についてのメッセージは、コンソールウィンドウに表示されます。メッセージ行をダブルクリックすると、不定値となった代入行が表示されます。

結論

Active-HDL は、シミュレーションの初心者にも経験者にも有効なツールです。 メニューからコマンドを選択して実行するのが好きなユーザもいれば、ショートカットキーが使いやすいと思うユーザもいます。最初はまずメニューから実行し、習熟するにつれてショートカットキーを使ってください。一般的にショートカットキーは、ツール操作を最速に行う方法です。

ここで紹介したように Active-HDL は、デザインのエラーを効果的にデバッグするための多くのオプションを提供しています。これらのデバッグツールはHDLコードのチェックを制限することはなく、デザインのビヘイビアを効果的に検証することができます。Active-HDLには、HDLコードやプロセス、プロシージャの希望の構文をトレースする多くのオプションがあります。信号の振る舞いをトレースしたり、シミュレーション結果を確認し、ファイルに保存するオプションもあります。さらに Active-HDLでは、ユーザが指定した条件に達した時いつでもシミュレーションを停止することができます。HDLコードにブレークポイントを設定して、指定行の実行時にシミュレーションを停止することもできます。Active-HDL の環境はインタラクティブなので、シミュレーション実行中にデバッグ機能を起動することができます。

最後に、本アプリケーションノートで紹介しているすべてのデバッグツールは、オンラインモード (実時間のシミュレーション)で動作するため、デバッグツールを使った大きなデザインのデバッグは、 時間の非効率的な使用につながります。そのような損失を排除するには、ポストシミュレーションデバッグと呼ばれるオフラインモードのデバッグツールを利用します。ポストシミュレーションデバッグは、シミュレーション終了後でもデバッグのためにシミュレーション結果を観測することができる先進的な機能で、シミュレーションのどの時点でも繰り返しコードをデバッグすることができます。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.