Active-HDL における ALTERA NIOS II 組み込みプロセッサデザインの

シミュレーション方法

本アプリケーションノートでは、Active-HDL における ALTERA NIOS II 組み込みプロセッサデザインのシミュレーション方法を説明します。 ここでは Eclipse IDE for C/C++ Developers software のサンプルデザイン “Board Diagnostics” をベースにしていますが、基本フローは他のデザインでも同じです。

必要となるツール

本アプリケーションノートでは、次のツールをインストールしており、操作経験があることを前提としています。

-

Altera Quartus II 10.1 以降

-

NIOS II EDS 9.0 以降

-

Active-HDL 8.3 以降

デザインの設定

-

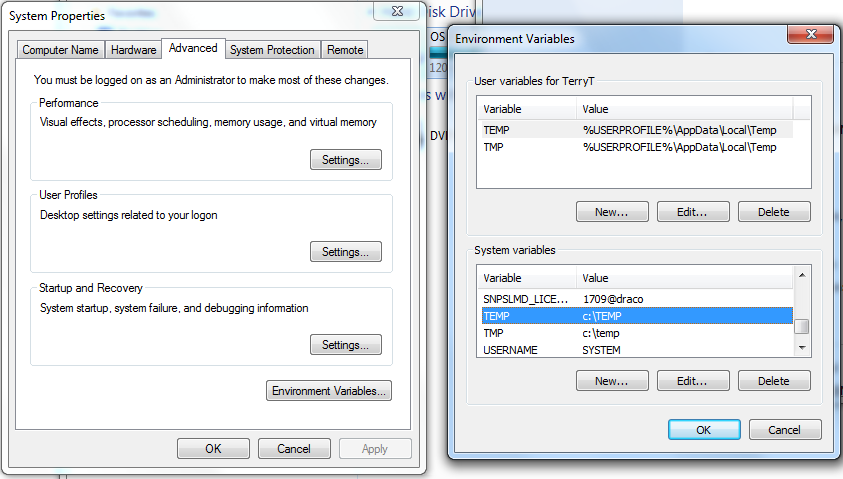

“C:\” ルートデイレクトリに空の “TEMP” フォルダを作成します。コンピュータのコンテキストメニューからプロパティ | システムの詳細設定を選択し、詳細設定タブにて環境変数ボタンをクリックします。下記のようにシステム環境変数 TEMP と TMP を設定します。

図 1: 環境変数の設定

-

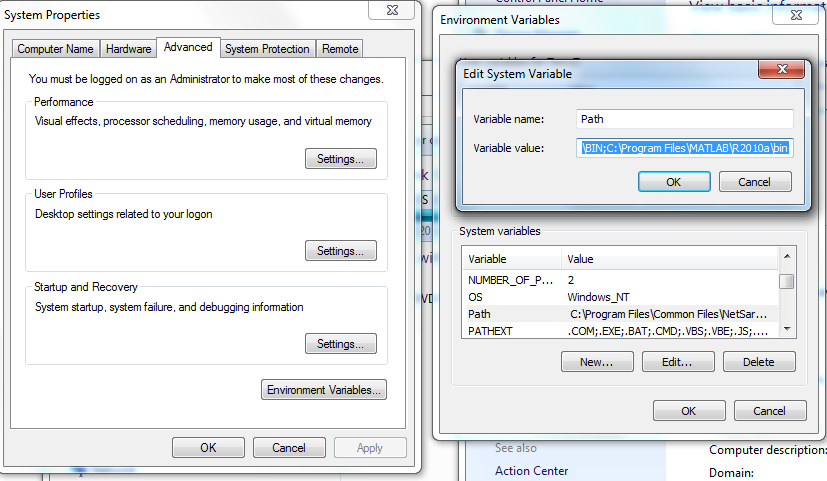

定義済みのシステム環境変数から Path を選択し、その変数値の設定欄にダブルセミコロン “;;” があるか確認し、ある場合には全ての “;;” をシングルセミコロン “;” に変更します。コンピュータを再起動します。

図 2: Path 整合性の確認

-

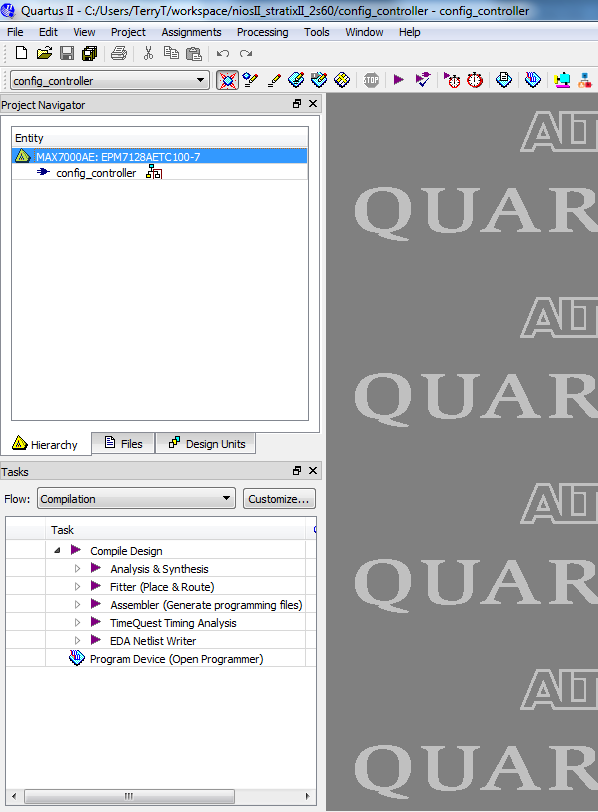

Quartus II を開きます。

-

File メニューから Open project を選択します。

-

プロジェクトディレクトリから任意の “.qpf” ファイルを選択して開くをクリックします。デザインが下記のように表示されます。

図 3: Quartus II Configuration Controller プロジェクト

SOPC Builder シミュレーション設定

-

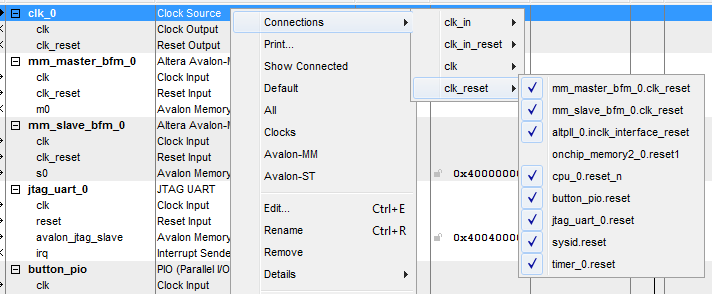

Quartus II にてプロジェクトを読み込んだ後、Tools メニューから SOPC Builder をクリックし、下記のようにデザインの全ての接続をチェックします。

図4: clk_0 clk_reset 接続例

-

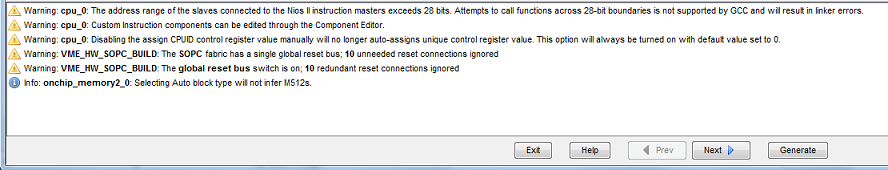

下記のようにエラーがないことを確認します。全てのワーニングやインフォメーションメッセージを読み、デザインへの影響を検討してください。

図 5: Design Status Window

シミュレーションファイルの生成

-

Next をクリックしてシミュレーションファイルを生成します。

-

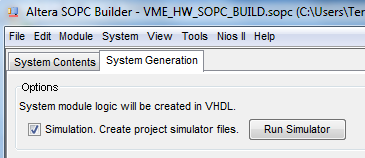

System Generation タブにて Simulation にチェックを入れ、プロジェクトシミュレータファイルを作成します。

図 6: System generation 設定

-

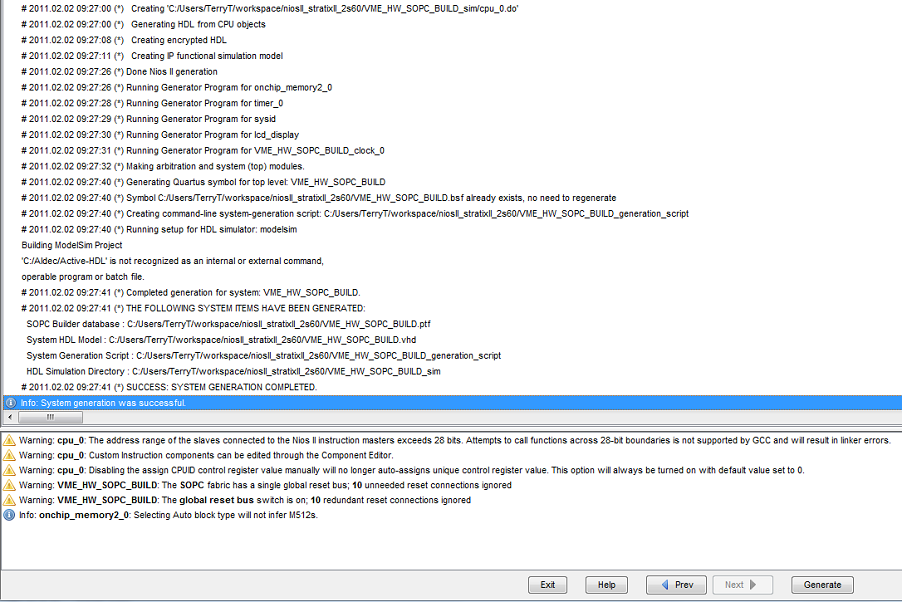

Generate ボタンをクリックします。変更箇所の保存を要求される場合には Save をクリックします。

図 7: Generate ボタン

図 8: ファイル生成の完了

ツールの構築とメモリ初期化ファイルの生成

Eclipse にてプロジェクトを作成し構築するには、次の手順で行います。

-

Tools メニューから NIOS II Software Build Tools for Eclipse を選択します。

-

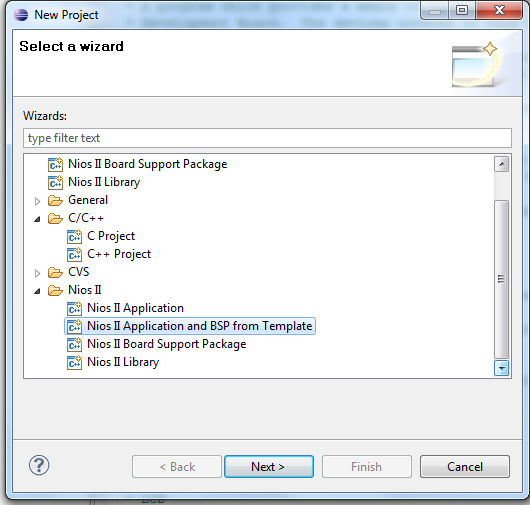

File | New| Project を選択します。

-

NIOS II Application and BSP from Template を選択して Next をクリックします。

図 9: NIOS II IDE にて新しいプロジェクトを作成

-

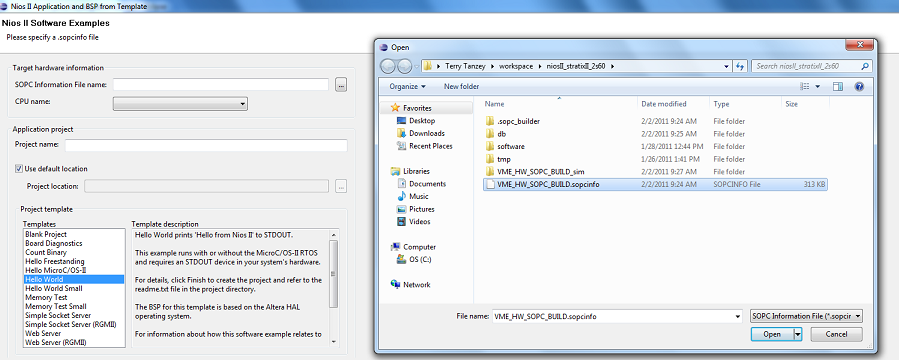

次のウィンドウで、SOPC 情報ファイルを探して Open をクリックします。

図 10: SOPC 情報ファイルの選択

-

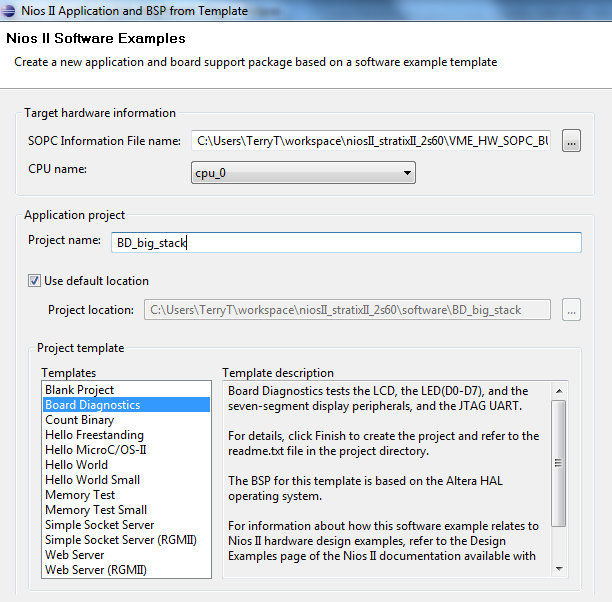

Board Diagnostics プロジェクトテンプレートを選択して、プロジェクトに “BD_big_stack” と名前を付けます。“Next” をクリックします。

注意: HAL BSP はメモリ管理ユニット (MMU) をサポートしていなため、Eclipse NIOS II サンプルを使用するには、MMU をデザインから除外する必要があります。

図 11: 新プロジェクトの設定

-

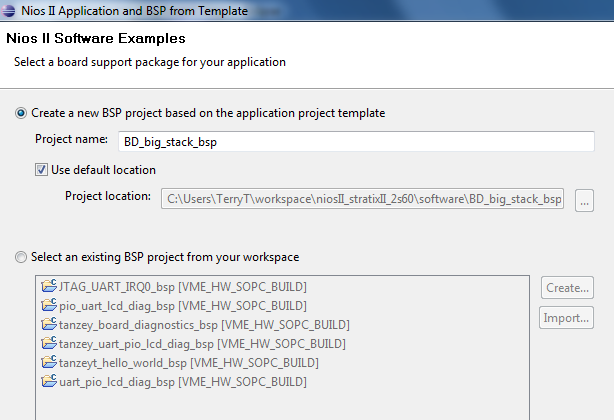

Create a new BSP project based ......を選択し、次のように設定します。“Finish” をクリックして、status ウィンドウが完了するのを待ちます。

図 12: BSP の生成

-

プロジェクトの生成をチェックし、status ウィンドウの出力が下記のようであることを確認します。

-

*** Clean-only build of configuration Nios II for project BD_big_stack ****

make clean

[BD_big_stack clean complete]

-

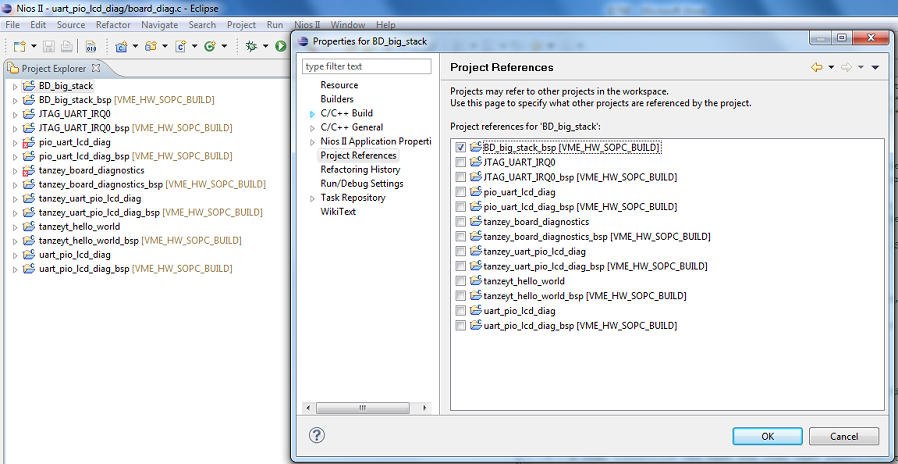

プロジェクトを選択し、マウス右ボタンメニューの Properties | Project References をクリックして、下記のような設定であることを確認します。OK をクリックします。

図 13: Project References

-

“BD_big_stack” プロジェクトを選択し、マウス右ボタンメニューの Build Project をクリックして実行します。出力ウィンドウをチェックします。プロジェクトによっては処理に時間がかかります。コンパイル処理が完了すると、プロジェクトディレクトリの .dat ファイルが更新されます。

--quartus_project_dir "C:/Users/TerryT/workspace/niosII_stratixII_2s60"

Info: (BD_big_stack.elf) 89 KBytes program size (code + initialized data).

Info: 31 KBytes free for stack + heap.

Info: Creating BD_big_stack.objdump

nios2-elf-objdump --disassemble --syms --all-header --source BD_big_stack.elf >BD_big_stack.objdump

[BD_big_stack build complete]

ソフトウェアプロジェクトの作成と構築が完了したら、シミュレーションを実行するために Active-HDL で下記の操作をします。

Active-HDL でのシミュレーションの実行

SOPC と Eclipse でのシミュレーションファイルの生成が完了したら、下記を実行します。

-

Active-HDL を起動します。Active-HDL がすでに立ち上がっている場合には、開いているワークスペースを閉じます。

-

メニューの File | Import | Altera SOPC Simulation Script を選択します。

-

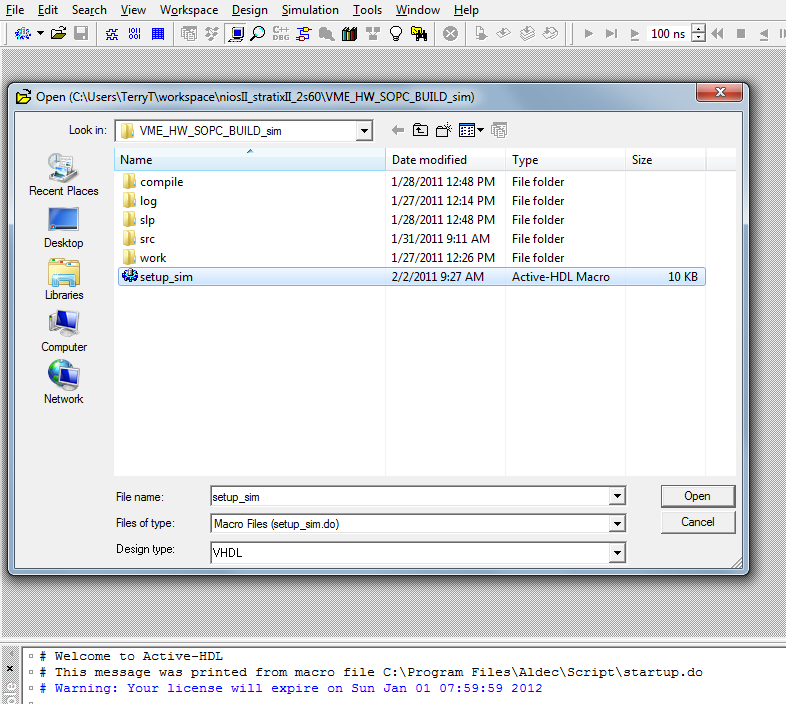

setup_sim.do ファイルを選択し、Open をクリックします。[setup_sim.do ファイルはプロジェクトディレクトリに存在します。このファイルは SOPC builder により生成されています。]

図 14: setup_sim.do ファイル

-

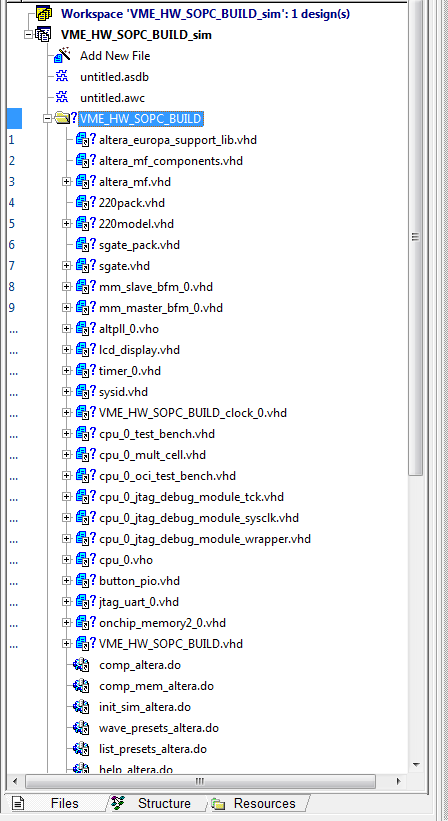

Altera SOPC Simulation Script importing ウィザードにより、ワークスペースが作成され、必要な do ファイルが作成されて、ワークスペースに付加されます。下記は setup_sim.do ファイルインポート時の典型的なコンソール出力です。シミュレーションスクリプトを Active-HDL にインポートすると、ワークスペースは下記のようになります。

# ELBREAD: Elaboration time 2.5 [s].

# Reading "setup_sim.do" ...

# Creating "setup_sim_altera.do" ...

# Creating "comp_altera.do" ...

# Creating "comp_mem_altera.do" ...

# Creating "init_sim_altera.do" ...

# Creating "wave_presets_altera.do" ...

# Creating "list_presets_altera.do" ...

# Creating "help_altera.do" ...

# Creating "aliases_altera.do" ...

# Creating "jtag_uart_0_log_altera.do" ...

# Import process successfully finished, etc.

図15: setup_sim.do ファイルインポート後のワークスペース

-

comp_altera.do ファイルを実行して、必要なライブラリのマッピングとコンパイルを行います。 マクロファイルを実行するには、comp_altera.do を選択し、マウス右ボタンメニューの execute をクリックします。

# Compile Architecture "europa" of Entity "onchip_memory2_0_s1_arbitrator"

# Compile Entity "sysid_control_slave_arbitrator"

# Compile Architecture "europa" of Entity "sysid_control_slave_arbitrator"

# Compile Entity "timer_0_s1_arbitrator"

# Compile Architecture "europa" of Entity "timer_0_s1_arbitrator"

# Compile Entity "VME_HW_SOPC_BUILD_reset_clk_0_domain_synch_module"

# Compile Architecture "europa" of Entity "VME_HW_SOPC_BUILD_reset_clk_0_domain_synch_module"

# Compile Entity "VME_HW_SOPC_BUILD_reset_altpll_0_c0_out_domain_synch_module"

# Compile Architecture "europa" of Entity "VME_HW_SOPC_BUILD_reset_altpll_0_c0_out_domain_synch_module"

# Compile Entity "VME_HW_SOPC_BUILD"

# Compile Architecture "europa" of Entity "VME_HW_SOPC_BUILD"

# Compile Entity "test_bench"

# Compile Architecture "europa" of Entity "test_bench"

# Compile success 0 Errors 0 Warnings Analysis time : 0.8 [s]

-

init_sim_altera.do ファイルを実行し、イニシャライズシミュレーション処理を行います。次のメッセージがコンソールに表示されます。

# ELAB2: Elaboration final pass...

# ELAB2: Create instances ...

# ELAB2: Create instances complete.

# SLP: Started

# SLP: Elaboration phase ...

# SLP: Elaboration phase ... skipped, nothing to simulate in SLP mode : 0.0 [s]

# SLP: Finished : 0.0 [s]

# ELAB2: Elaboration final pass complete - time: 1.2 [s].

# KERNEL: Kernel process initialization done.

# Allocation: Simulator allocated 25170 kB (elbread=6156 elab2=16989 kernel=2025 sdf=0)

# KERNEL: ASDB file was created in location C:\Users\TerryT\workspace\niosII_stratixII_2s60\VME_HW_SOPC_BUILD_sim\src\wave.asdb

# 11:36 AM, Wednesday, February 02, 2011

# Simulation has been initialized

# Selected Top-Level: test_bench (europa)

-

wave_presets_altera.do ファイルを実行し、信号を波形に追加します。

-

simulation メニューからシミュレーションを実行するか、コンソールに run 1000 us とタイプして enter キーを押します。コンソールには次のメッセージが表示されます。

# # Displays virtual signals

# 6 signal(s) traced.

run 1000 us

# EXECUTION:: NOTE : Stratix II GX PLL is enabled

# EXECUTION:: Time: 0 ps, Iteration: 2, Instance: /DUT/the_altpll_0/altpll_0_altpll_sd1_183/STRATIXII_ALTPLL/M1, Process: SCHEDULE.

# EXECUTION:: NOTE : Stratix II GX PLL locked to incoming clock

# EXECUTION:: Time: 110 ns, Iteration: 4, Instance: /DUT/the_altpll_0/altpll_0_altpll_sd1_183/STRATIXII_ALTPLL/M1, Process: SCHEDULE.

# KERNEL: stopped at time: 1 ms

-

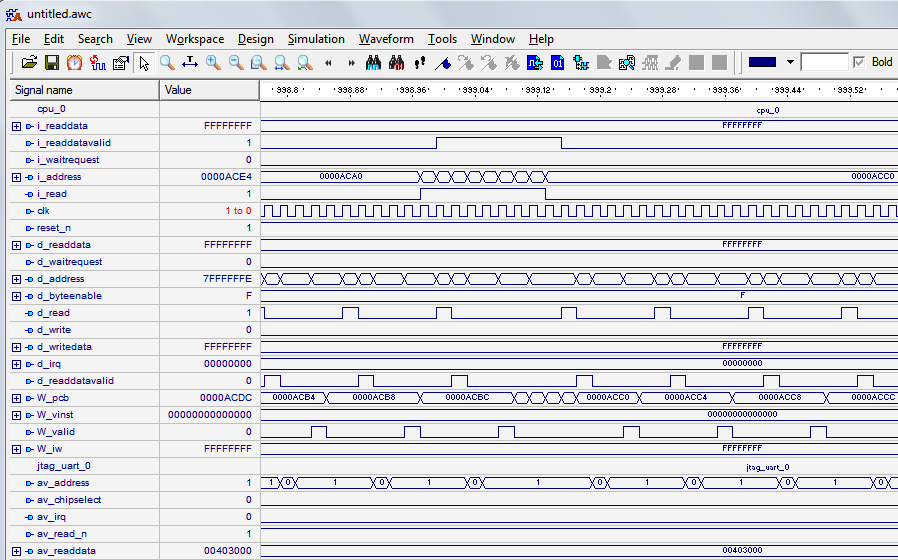

下記は 1msec のシミュレーション実行結果の例です。

図16: Active-HDL シミュレーション実行

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.