Active-HDLとXilinx System Generator

Active-HDL System Generatorのインターフェイスは、 Xilinx System GeneratorにカスタムHDLモデルを組み込む方法を提供します。これは、Active-HDLでカスタムHDLブロックをMathworkのSimulinkとXilinx System Generatorブロックで協調検証することを可能にします。

Xilinx System Generator/Black Box helpで仕様と制限を確認し、クロッキングとデータタイプ、エンティティ/モジュールのコーディングに関する特別なルールに注意してください。

Active-HDLでVHDLモデルの準備

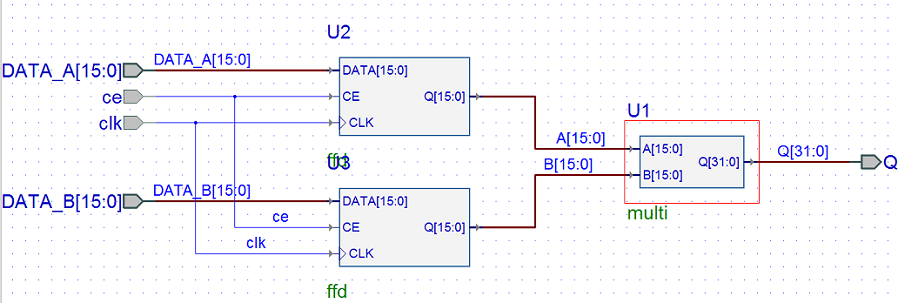

Active-HDLのIPコア・ウィザードを使用して、clocked_multiplierのデザインを作成します。下図はActive-HDLで作成されたBDE回路図ファイルのclocked_multiplier.bdeを示しています。

ffd VHDL code:

library IEEE; use IEEE.std_logic_1164.all; entity ffd is port ( CE : in std_logic; CLK : in std_logic; DATA : in std_logic_vector(15 downto 0); Q : out std_logic_vector(15 downto 0) ); end entity; --}} End of automatically maintained section architecture ffd_arch of ffd is begin process (CLK) begin if rising_edge(CLK) then if CE = '1' then Q end if; end if; end process; end ffd_arch;

multi VHDL code:

library IEEE; use IEEE.std_logic_1164.all; entity multi is port ( A : in std_logic_vector(15 downto 0); B : in std_logic_vector(15 downto 0); Q : out std_logic_vector(31 downto 0) ); end multi; --}} End of automatically maintained section library IEEE; use IEEE.std_logic_signed.all; architecture multi_arch of multi is begin Q end multi_arch;

clocked_multiplier VHDL code:

library IEEE; use IEEE.std_logic_1164.all; entity clocked_multiplier is port( ce : in STD_LOGIC; clk : in STD_LOGIC; DATA_A : in STD_LOGIC_VECTOR(15 downto 0); DATA_B : in STD_LOGIC_VECTOR(15 downto 0); Q : out STD_LOGIC_VECTOR(31 downto 0) ); end clocked_multiplier; architecture clocked_multiplier of clocked_multiplier is ---- Component declarations ----- component ffd port ( CE : in STD_LOGIC; CLK : in STD_LOGIC; DATA : in STD_LOGIC_VECTOR(15 downto 0); Q : out STD_LOGIC_VECTOR(15 downto 0) ); end component; component multi port ( A : in STD_LOGIC_VECTOR(15 downto 0); B : in STD_LOGIC_VECTOR(15 downto 0); Q : out STD_LOGIC_VECTOR(31 downto 0) ); end component; ---- Signal declarations used on the diagram ---- signal A : STD_LOGIC_VECTOR (15 downto 0); signal B : STD_LOGIC_VECTOR (15 downto 0); begin ---- Component instantiations ---- U1 : multi port map( A => A, B => B, Q => Q ); U2 : ffd port map( CE => CE, CLK => CLK, DATA => DATA_A, Q => A ); U3 : ffd port map( CE => CE, CLK => CLK, DATA => DATA_B, Q => B ); end clocked_multiplier;

Active-HDLで協調シミュレーションのための準備

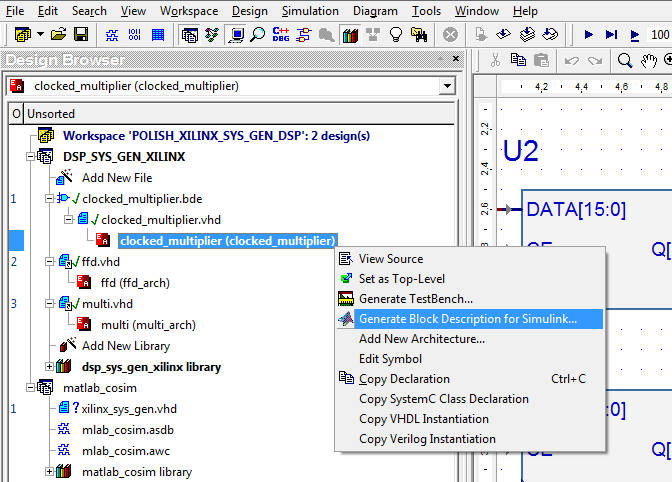

MATLABのSimulink環境での協調シミュレーション・プロセスを開始するために、まずHDLモデルのトップレベルのエンティティまたはモジュール用のSimulink記述ファイル(.m)を生成する必要があります。 Active-HDLは、自動的にこれを行うことが出来ます。Active-HDLで次の手順を実行します:

-

ワークスペースを開き、協調シミュレーションを行うHDLユニットを含むデザインをアクティブにします。

-

Simulinkで協調検証を行おうとしているモデルを表すHDL ファイルをコンパイルします (本ケースでは、clocked_multiplier.vhd)。

-

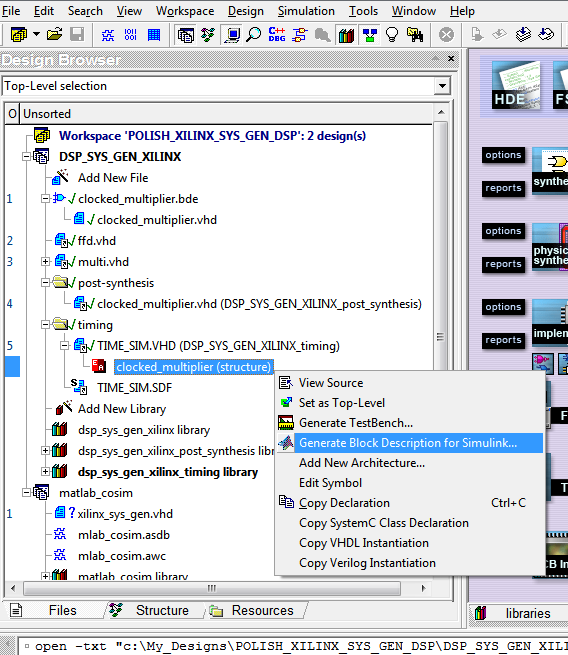

Simulinkでの HDL ブラックボックスとして使用されるトップレベルのデザインユニットが含まれているソースファイル (例: clocked_multiplier.vhd) を展開します。 このユニット(例: clocked_multiplier(clocked_multiplier)) を右クリックし、ポップアップメニューからGenerate Block Description for Simulink オプションを選択します。

このオプションは、設計ライブラリが空の場合は使用できません。

-

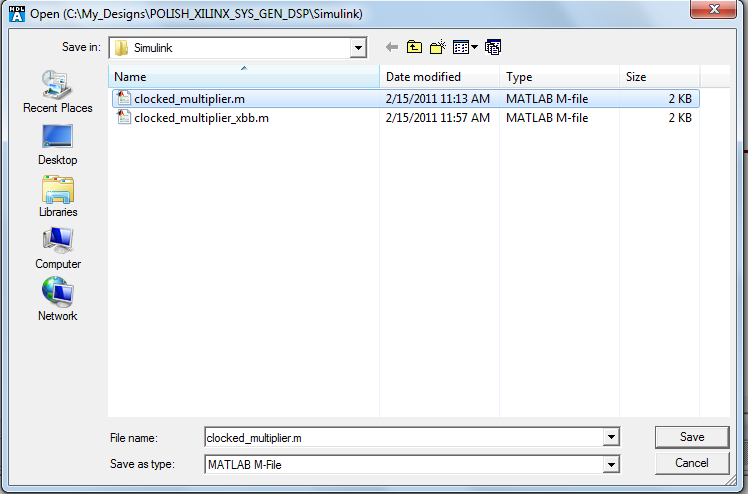

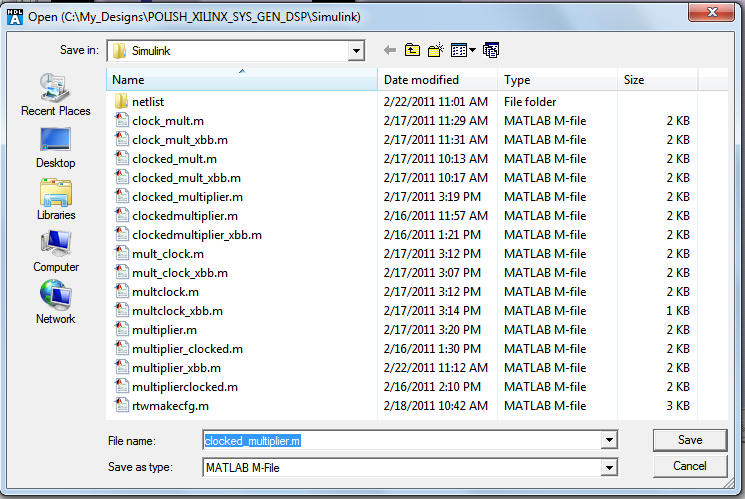

Saveを押して、MATLAB M-File 生成を完了します。

コンソールに次のメッセージが表示されます:

simulinkgenmod -f -o "C:\My_Designs\POLISH_XILINX_SYS_GEN_DSP\Simulink\clocked_multiplier.m" clocked_multiplier clocked_multiplier

# Generating block description file: 'C:\My_Designs\POLISH_XILINX_SYS_GEN_DSP\Simulink\clocked_multiplier.m'...

# Generation of block description file for "clocked_multiplier (clocked_multiplier)" completed successfully.

Pure System Generator デザイン

-

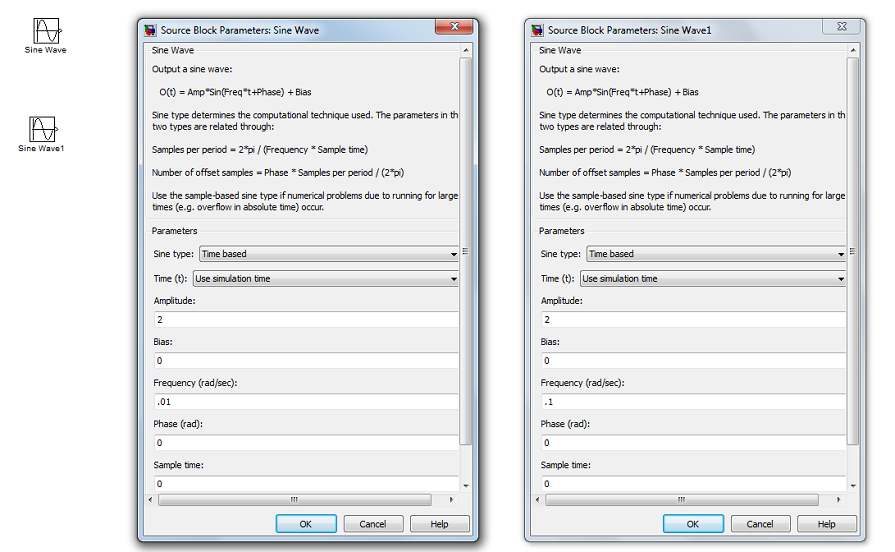

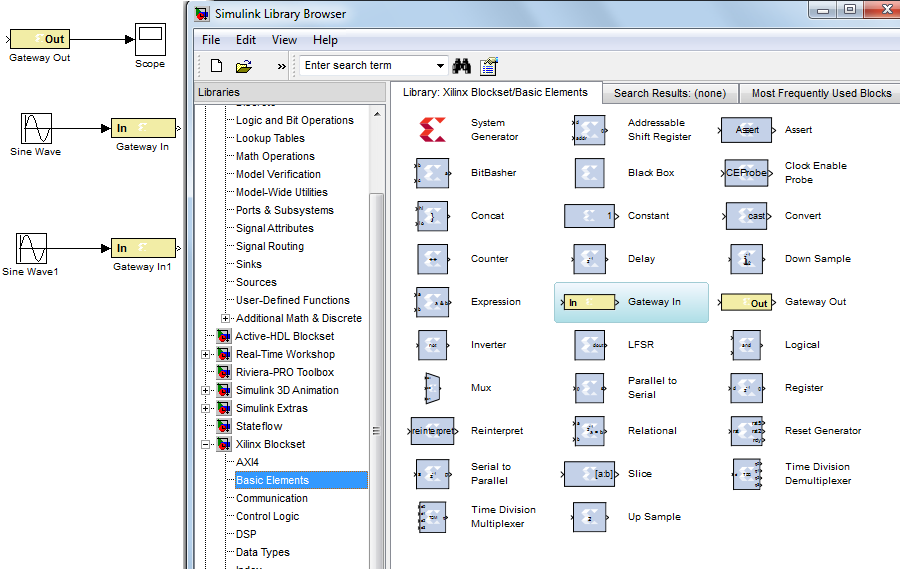

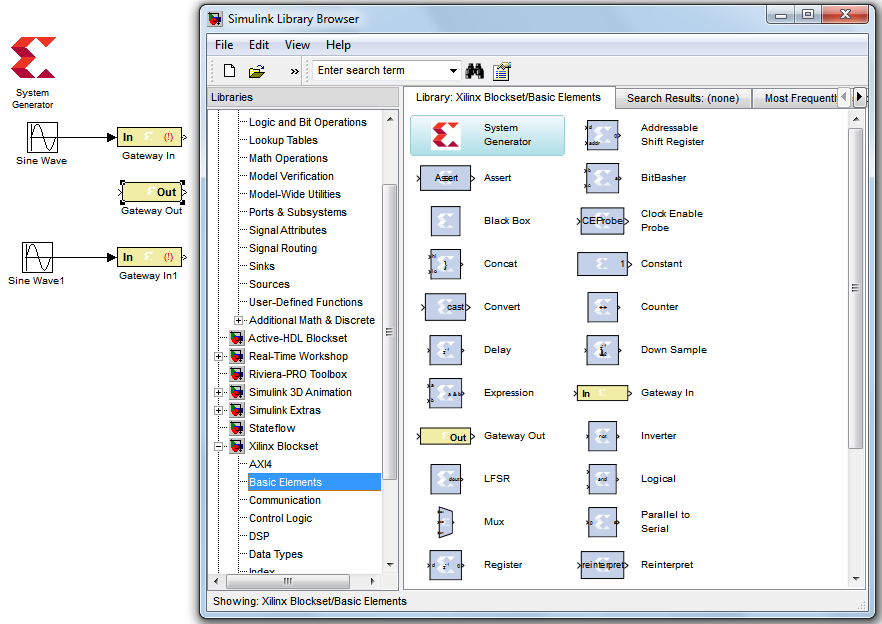

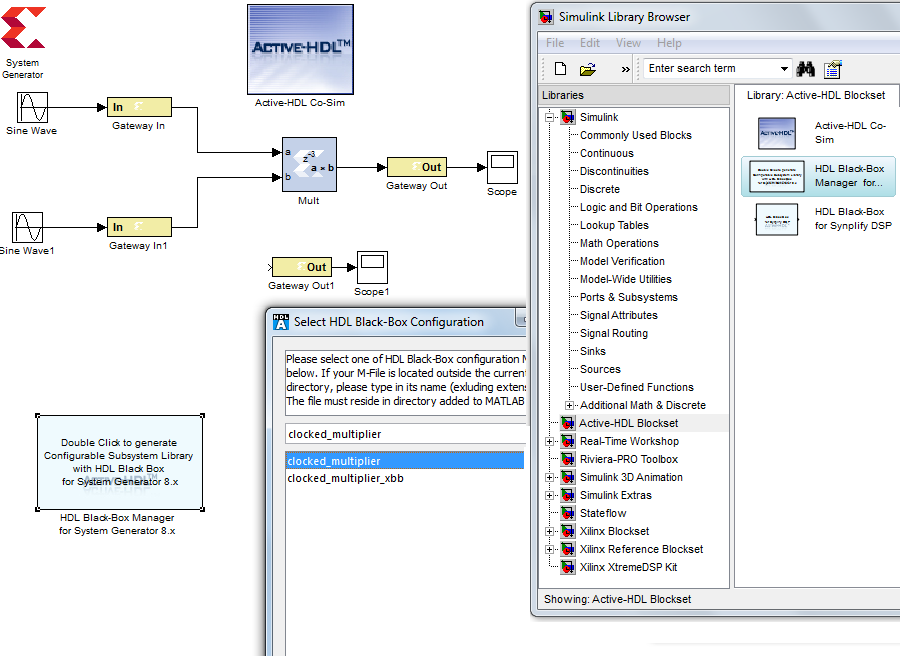

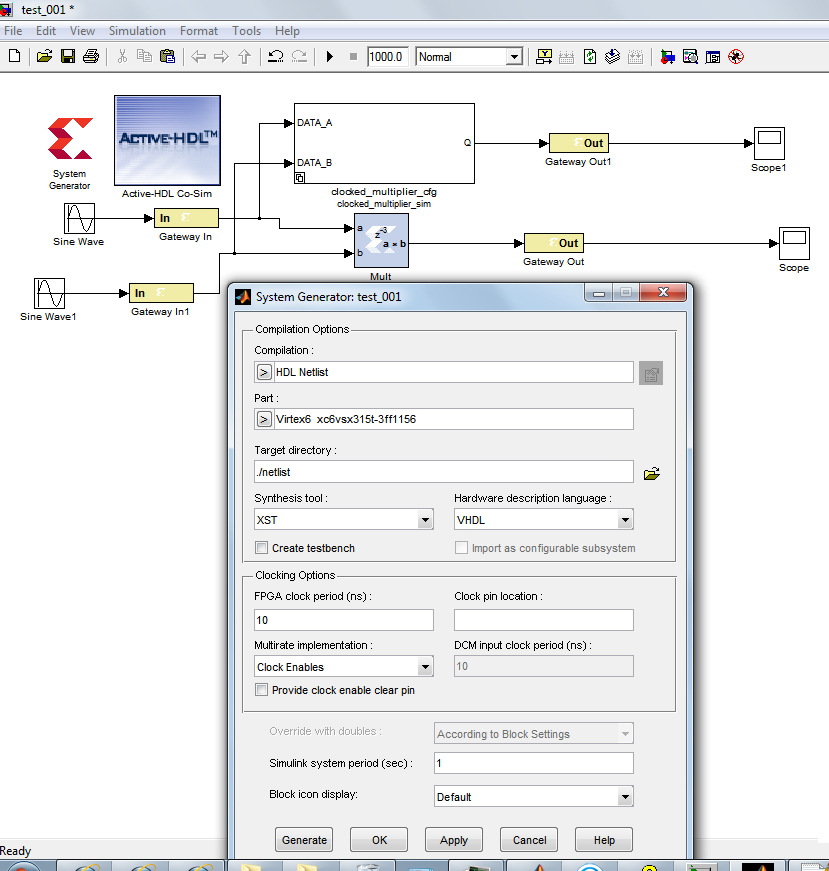

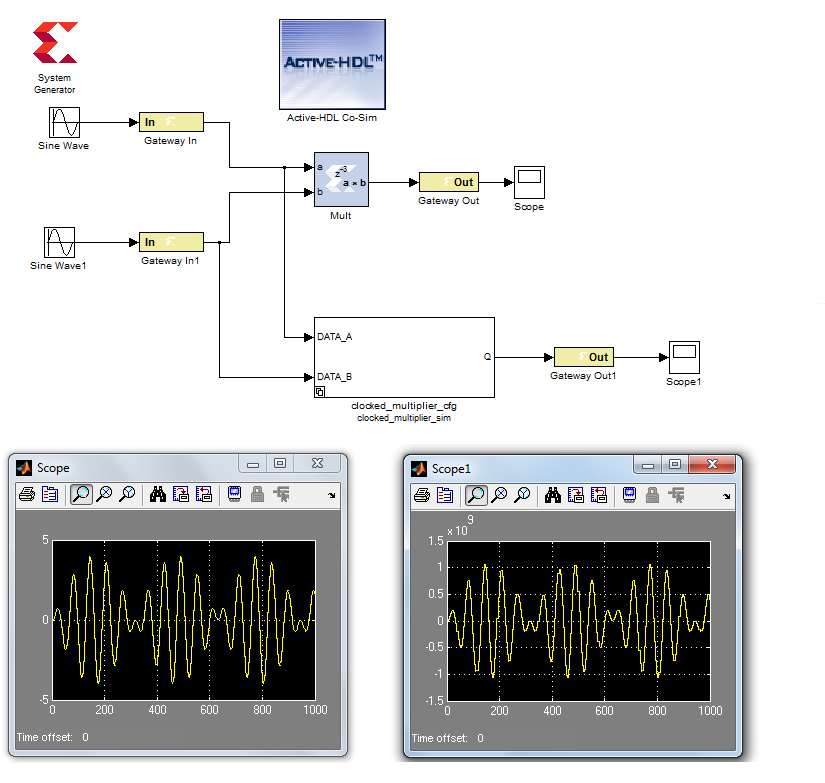

新しいMATLAB SIMULINKモデルを開き、下図に示された項目を追加し始めてください。signal generatorsから始めて、下記に示したパラメータを使用してください。

-

Gatewayとscopeを追加し、図のように接続します

-

Xilinx System Generatorを追加し、下記に示したパラメータを使用してください。

-

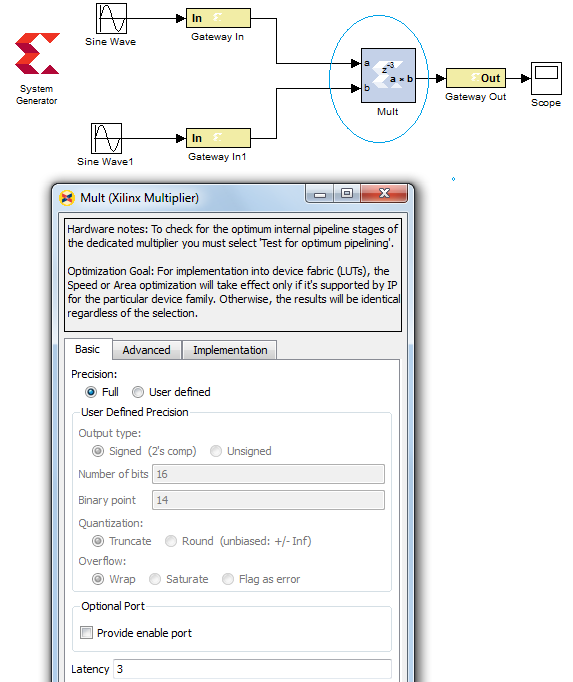

Xilinx Multiplier Blockを追加し、下図に示されたすべての接続、パラメータを設定してください。

-

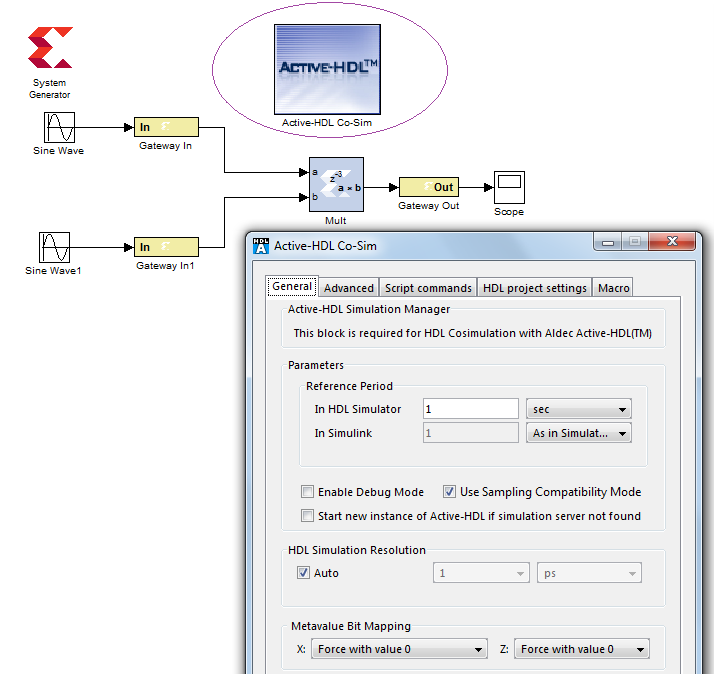

Active-HDL Co-simulation Block 追加し、下記に示したパラメータを使用してください。

-

Active-HDL System Generation Black Box を追加後、以前生成した".m"ファイルを使用しOKをクリックします。

-

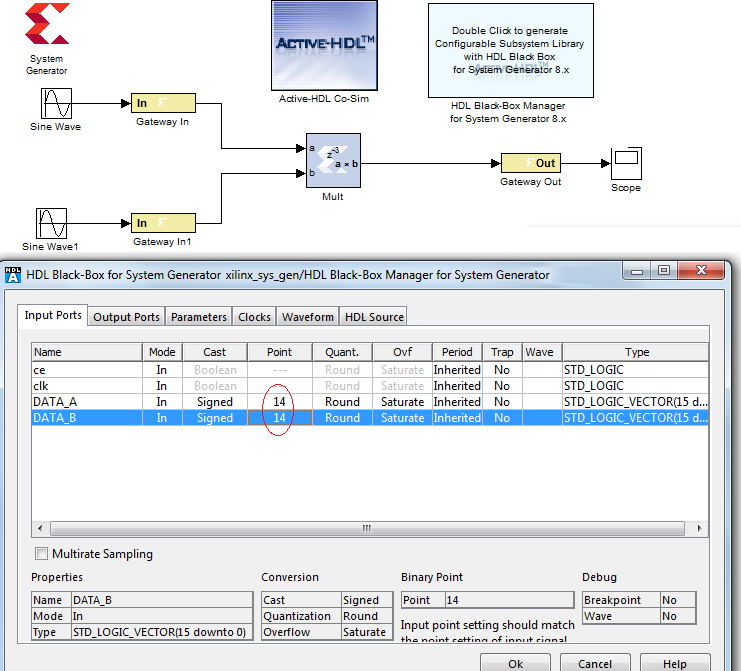

自動的に開かない場合は、ボックスを表示するためにActive-HDL System Generation Black Box をクリックします。Input Ports タブを選択し表示された内容に変更します。

-

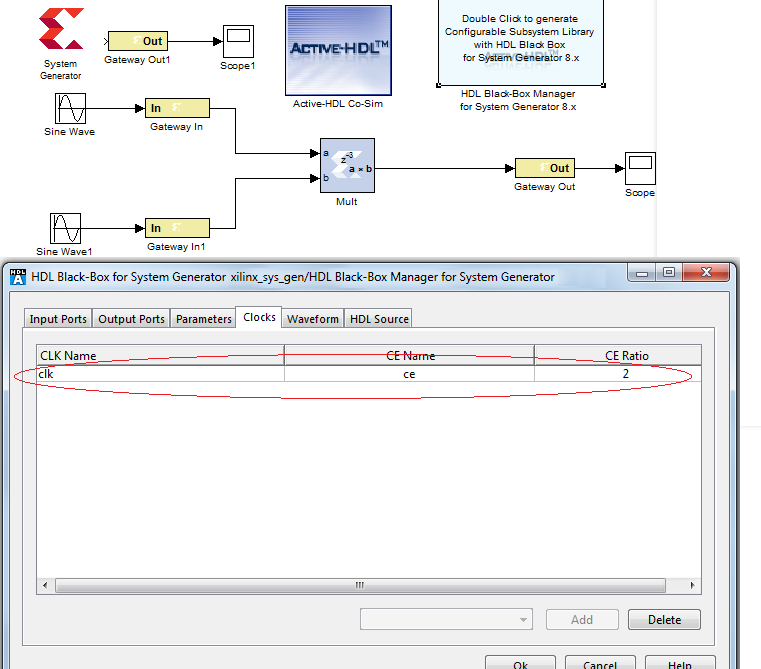

Active-HDL System Generation Black Box の Clocks タブを選択し、clock とclock_enable の両方のソースを挿入するためにAdd をクリックします。

-

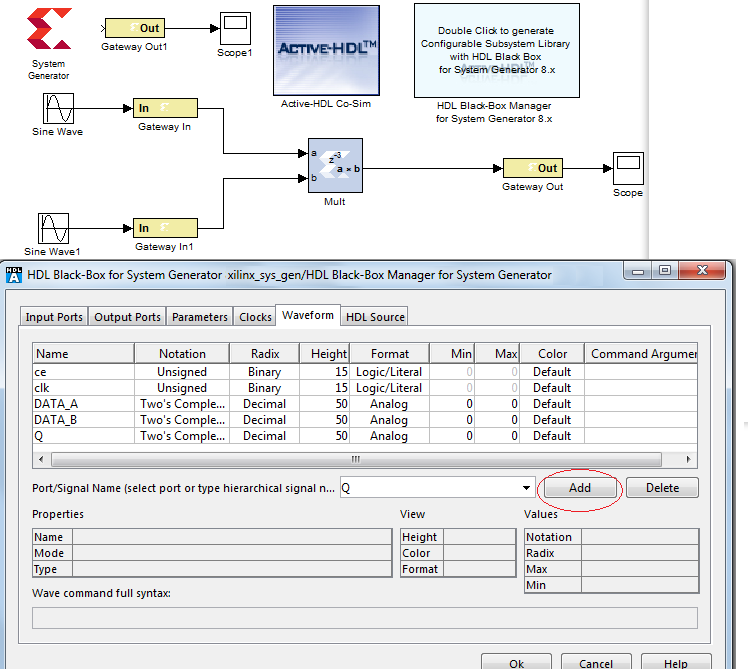

Active-HDL System Generation Black Box のWaveform タブを選択し、選択した波形を挿入 (Active-HDL内で表示用)するためにAdd をクリックします。

-

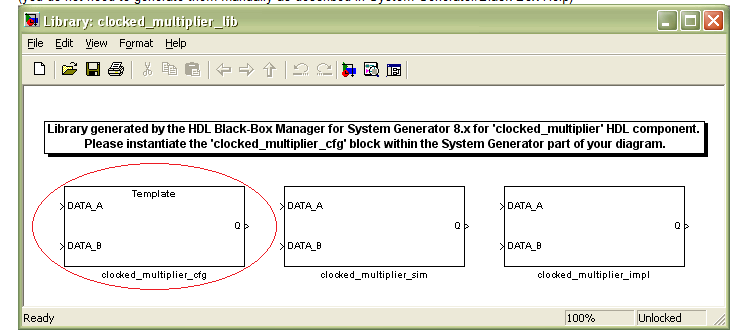

Active-HDL System Generation Black Box の全ての変更を適用するためにOK をクリックします。3つのボックスが表示されますが1つのみ使用します。"_cfg" ブロックを選択し、全ての接続場所が適切になるようにモデル内にそれを挿入します。モデルからActive-HDL System Generation Black Box を削除します。

-

追加したブロック上で左クリックし、Xilinx System Generator を開き、モデルで使用する全てのXilinx パーツのビルドを実行するためにGenerate タブをクリックします。

-

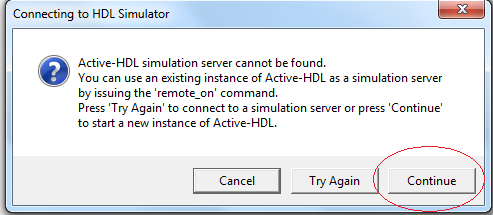

MATLAB SIMULINK シミュレーションを実行し、 “CONTINUE” ボタンをクリック後にActive-HDL は自動的に起動します。Active-HDL のロード前の質問をステップの後、クライアント接続が確立されシミュレーションが完了するまで実行されます。

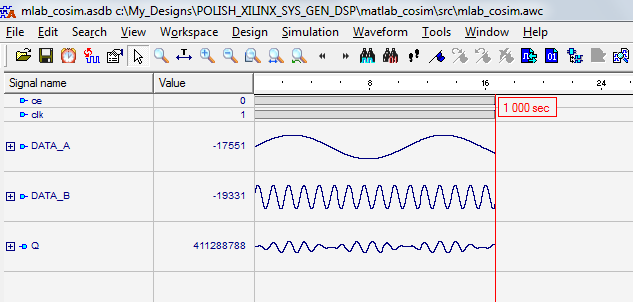

協調シミュレーションは実行され、モデルは100msecまたは選択された所望の実行時間まで実行されます。

-

Active-HDL のwaveforms を確認します。

-

モデルを実行してから、scope の結果を確認します。 それらが同一であることを保証するためにディスプレイを比較してください。

Active-HDLでデザインの合成

-

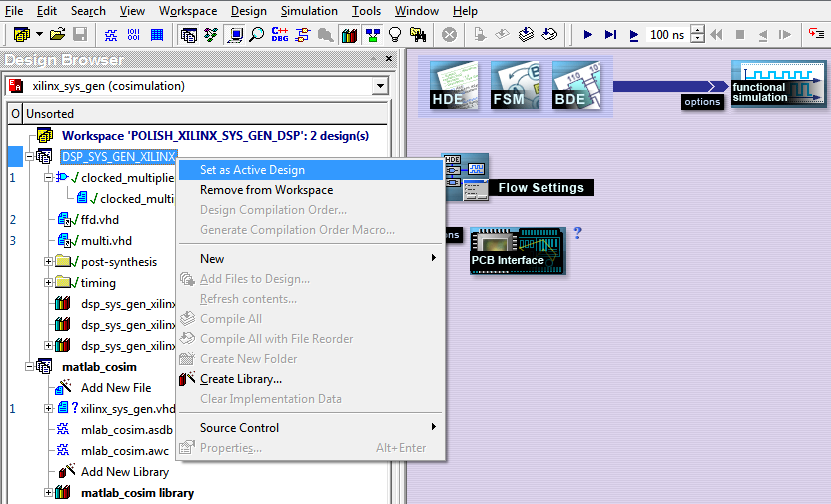

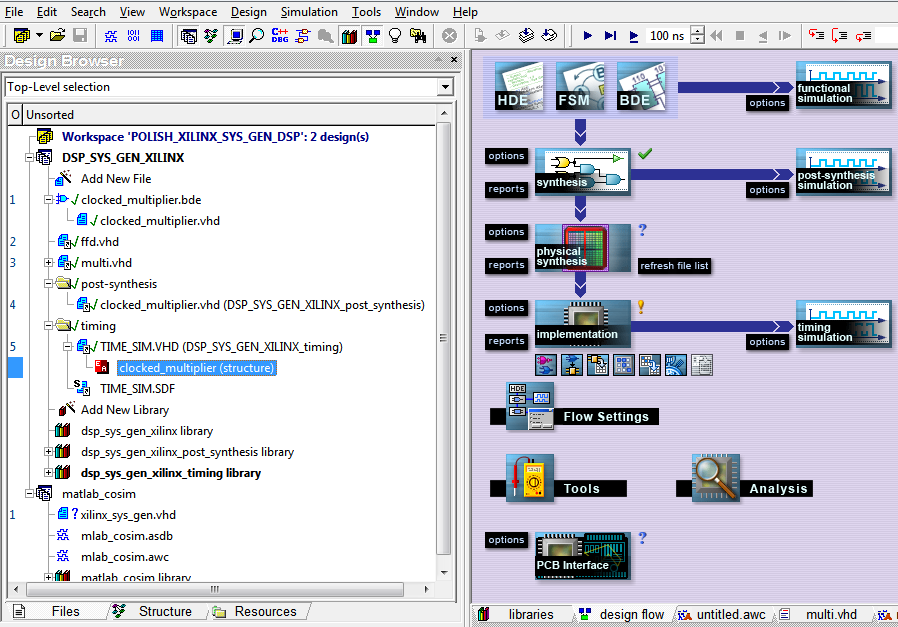

MATLAB SIMULINK モデルを閉じ、Active-HDL に戻り、図の様にデザインをアクティブに設定します。

-

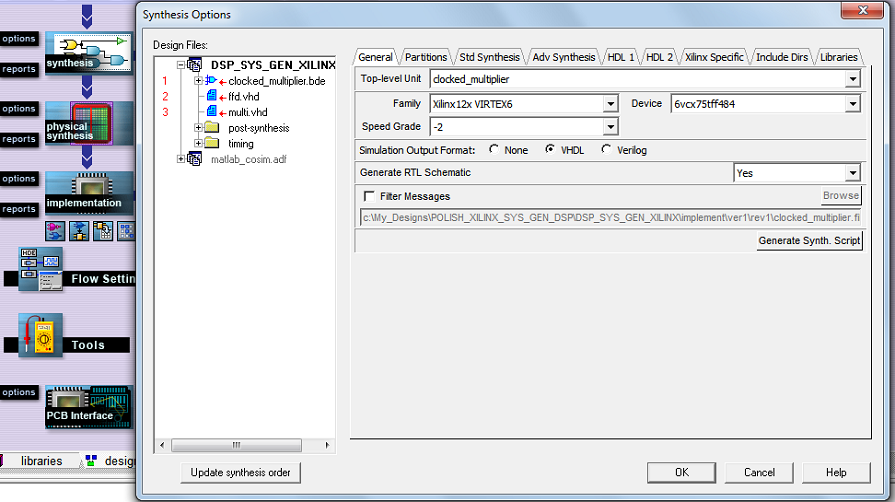

図の様にFPGAデバイス、およびデザインのトップレベルを選択するために Xilinx Synthesis Options を設定します。

-

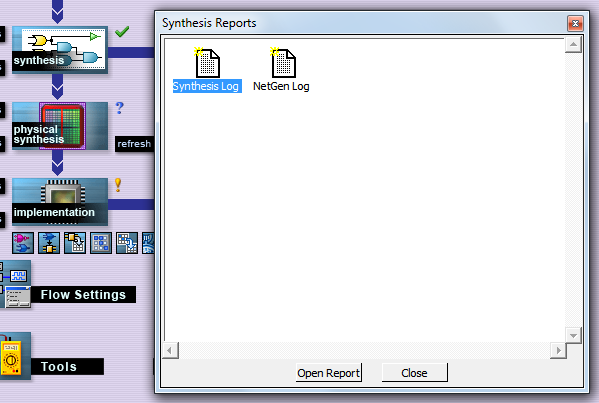

デザインを合成、エラーやワーニング等をログレポートで確認します。

-

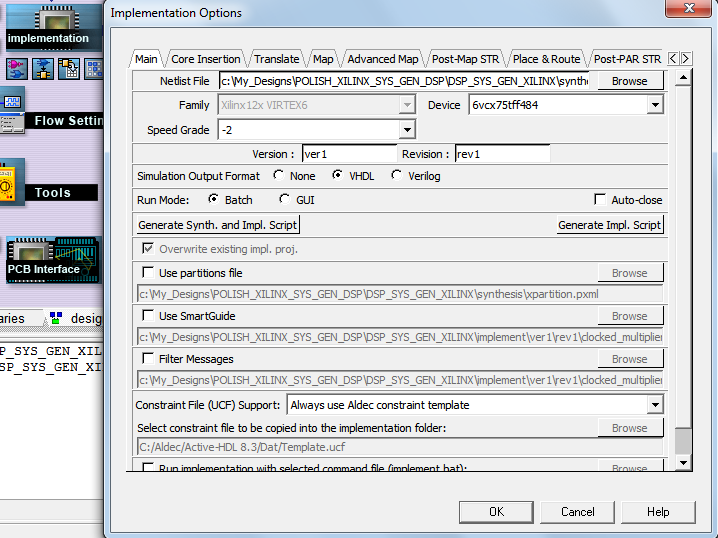

Xilinx Implementation Options を選択し、図の様にSimulation Output Format でVerilog またはVHDL を設定します。

-

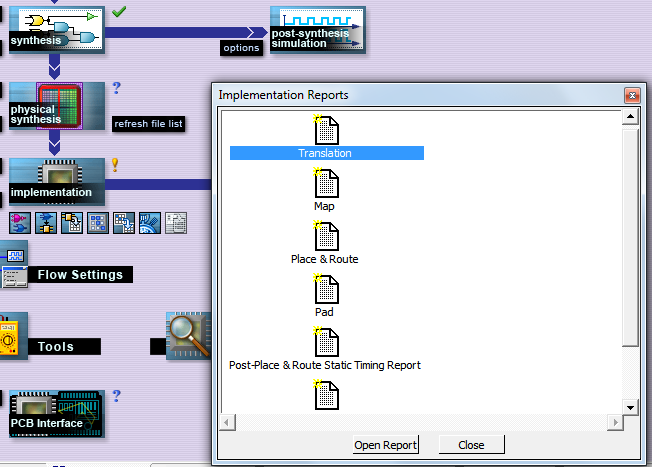

Floor Plannerを使用せずにデザインを配置配線し、エラーやワーニング等をログレポートで確認します。

Active-HDLでXilinxのタイミングファイルを使用した協調シミュレーションを行うための準備

-

TIME_SIM.VHD を開き、ファイルの最後にあるROC_WIDTH を下記の様にミリ秒単位の値に変更します。

NlwBlockROC : X_ROC generic map (ROC_WIDTH => 100 ms) --match this value port map (O => GSR); NlwBlockTOC : X_TOC port map (O => GTS); -

図に示すとおり、Xilinx Synthesis & Implementation プロセスが加えた Active-HDL の追加デザインファイルをコンパイルしてください。必要なタイミングライブラリを設定し、下記の様にentity/architectureのペアを選択します。

-

Simulink でHDL ブラックボックスとして使用されているトップレベルのデザインユニットが含まれているソースファイル (例: TIME_SIM.VHD) を展開します。このユニット (例: clocked_multiplier(structure)) を右クリックし、ポップアップメニューからGenerate Block Description for Simulink オプションを選択します。

-

Save を押して、 MATLAB M-File generation を完了します。

コンソールに次のメッセージが表示されます:

simulinkgenmod -f -o "C:\My_Designs\POLISH_XILINX_SYS_GEN_DSP\Simulink\clocked_multiplier.m" clocked_multiplier structure

# Generating block description file: 'C:\My_Designs\POLISH_XILINX_SYS_GEN_DSP\Simulink\clocked_multiplier.m'...

# Generation of block description file for "clocked_multiplier (structure)" completed successfully.

-

Xilinxタイミングファイルから生成された新しい".m"ファイルを使用して、 Pure System Generator Design のためにステップを繰り返してください。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.