Xilinx CORE Generatorで利用可能なAXI BFMサンプルのシミュレーション

ISE CORE Generatorは、Xilinx FPGA用に最適化およびパラメータ化されたコアを生成するデザインエントリーツールです:

-

アーキテクチャ固有、ドメイン固有 (組込み、コネクティビティとDSP)、およびマーケット固有IP (オートモーティブ、コンシューマ、軍事/航空、通信、放送など) が含まれます。

-

ユーザーがカスタマイズ可能なIP機能は、メモリやFIFOなどの一般的に使用される機能から、フィルタや変換などのシステムレベルのビルディングブロックまで、さまざまな複雑性を持っています。

-

各コアの詳細情報(データシート、ユーザーガイド、リリースノート、ライセンス)。

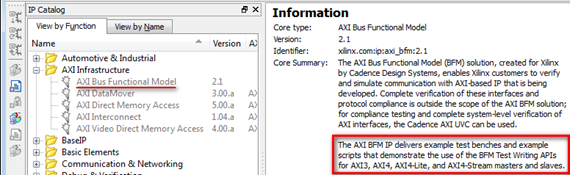

AXI BFM IPには、AXI3、AXI4、AXI4-Lite、およびAXI4-Stream マスタ/スレーブ BFMペアの機能を示すサンプルとテストベンチが付属しています。これらのサンプルは、AXI3、AXI4、AXI4-Lite、およびAXI4-Streamの各インターフェースを用いたカスタムRTLデザインのテストを行う際の開始点として使用できます。サンプルには、CORE Generatorの「IP Catalog-View by Function-AXI Infrastructure-AXI Bus Functional Model」からアクセスできます(図1)。

図 1. CORE GeneratorのAXI BFMのサンプル

AXI BFM IPは、CORE Generator IPカタログの "AXI Infrastructure "または "Debug & Verification "フォルダにあるAXI BFM IPを生成することで、サンプルやテストベンチを得ることができます。AXI BFM IPを生成すると、ユーザが指定した<コンポート名>ディレクトリが生成されます。このディレクトリには、シミュレーション環境の設定方法やサンプルの実行方法を説明したREADME.txtファイルが含まれています(simulate_aldecなどのベンダ固有のスクリプトは、simulation/functionalサブフォルダに用意されています)。

AXI BFMシミュレーションの実行方法の詳細については、Active-HDLでAXIベースデザインのシミュレーション、またはRiviera-PROでAXIベースデザインのシミュレーションを参照してください。

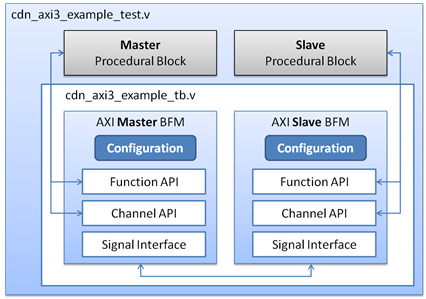

パッケージに含まれる最初のサンプルであるAXI3 BFMサンプルのテストベンチとテストを見てみましょう。本パッケージの他サンプルと同様に、このサンプルでもAXIマスタが1つのAXIスレーブに接続されており(図2)、コードのマスタ側とスレーブ側の両方が見えるようになっています。

図 2. テストベンチとテストケースの構造の例

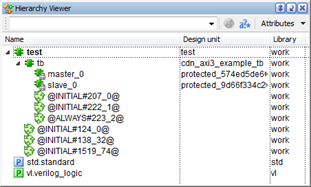

サンプルテスト(cdn_axi3_example_test.v)にはマスタとスレーブのコードが含まれており、ダイレクトテストを使用してマスタとスレーブ間でデータを転送を行い、シンプル、ループ、パラレルでの書き込みと読みだしのバースト転送など、さまざまなシナリオをシミュレートします。図3は、Riviera-PRO 2016.10に掲載されているこのデザインサンプルの階層を示しています(master_0とslave_0のユニットは暗号化されているため、ロック記号が付いていることに注意してください)。

図 3. テスト階層の例

基本的なテストの概念を説明するために、シンプルなループ書き込みと読み出しのバースト転送のシナリオを見てみましょう。次コードは,tb()の下でインスタンス化された実際のAXI BFMを構成するためのパラメータ宣言の一部を示しています:

//------------------------------------------------------------------------ // Module "test", AXI BFM Configuration - tb() //------------------------------------------------------------------------ parameter MASTER_NAME = "MASTER_0"; parameter SLAVE_NAME = "SLAVE_0"; parameter DATA_BUS_WIDTH = 32; /* ... Other parameters ... */ // Create an instance of the example tb cdn_axi3_example_tb #( MASTER_NAME, SLAVE_NAME, DATA_BUS_WIDTH, /* ... Other Parameters ... */) tb(); //------------------------------------------------------------------------ // Module "cdn_axi3_example_tb", Actual AXI BFM Instantiation //------------------------------------------------------------------------ cdn_axi3_slave_bfm #( SLAVE_NAME, DATA_BUS_WIDTH, ADDRESS_BUS_WIDTH, /* ... Other Parameters ... */) slave_0 (/* ... Actual Ports ... */);

そして次のマスタコードは、forループで3回の連続した書き込みと読み出しを行います。WRITE_BURSTとREAD_BURSTは標準的なAXI BFMチャネルレベルのAPIタスク(AXI Bus Functional Model User Guideで定義されています)であり、残りはルーチンチェックを実行する単なるサービスタスクです。

for (i = 0; i < 3; i = i + 1 ) begin // Full write transaction composed of multiple tasks: // - SEND_WRITE_ADDRESS, SEND_WRITE_BURST // - RECEIVE_WRITE_RESPONSE tb.master_0.WRITE_BURST( ..., test_data[i], ... ); // Service task checks if the return response is equal to OKAY tb.CHECK_RESPONSE_OKAY ( response ); // Full read transaction composed of SEND_READ_ADDRESS and RECEIVE_READ_BURST tasks tb.master_0.READ_BURST ( ..., rd_data, ... ); // Service task checks if response vector from READ_BURST is equal to OKAY (the vector // is created by concatenating all slave read responses together) tb.CHECK_RESPONSE_VECTOR_OKAY( vresponse, mtestBurstLength ); // Service task checks if the received data is equal to sent data tb.COMPARE_DATA( test_data[i], rd_data ); end

AXI BFMのユーザによる制御は、特定のAXI BFMコアインスタンスに対して、その階層名を用いて関数コールを行うことで実行されることに注意してください。例えば、WRITE_BURSTコマンドは、tb.master_0 AXI Master BFMでライトバーストトランザクションを開始し、アドレス、データ、その他の引数でライトバーストを実行するようコアを刺激します。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.