ユーザ定義のデザイン管理

概要

デフォルトでは、Active-HDL は固定のディレクトリ構造で全てのデザインファイルを管理しており、ブロック図やテキストファイル、波形およびスクリプトを /src フォルダに保存します。

version 9.2 からは、ユーザ定義のデザイン構造を設定することができるようになりました。これによりユーザは独自のディレクトリ構造を定義して、デザインファイルを保存することができます。 デザイン構造を定義すると、その後作成されたファイルや、外部からデザインに追加されたファイル、ブロック図やステートマシンから自動生成された HDL ファイルは、ユーザが定義したディレクトリに自動的に保存されます。例えば全ての HDLファイルは /hdl、ブロック図は /hds、波形ファイルは /wave フォルダなど。 ユーザはフォルダ名やパスを自由に定義できます。何も定義しない場合には、Active-HDL はデフォルトの固定ディレクトリ /src フォルダに全ファイルを保存します。

ユーザ定義のデザイン管理の利点

ユーザ定義のデザイン管理により、ローカルまたはリモートのチームベースで、FPGAプロジェクトの作成や管理が柔軟に行えます。

-

チーム全体または会社から要求されるデザイン構造に従うことができ、維持が容易です。

-

HDL ファイルを、ブロック図やテキスト、波形、スクリプト等の他の種類のファイルから分けて保存できます。

-

ファイルの種類や拡張子に応じて、ファイルを自動保存することができます。

-

ライブラリソースを他のデザインファイルから分離できます。

-

論理合成や配置配線ツールに合わせてディレクトリ構造を作成することができます。これによりFPGA開発の全工程で共通のデザイン構造を維持できます。

ユーザ定義のデザイン構造の作成

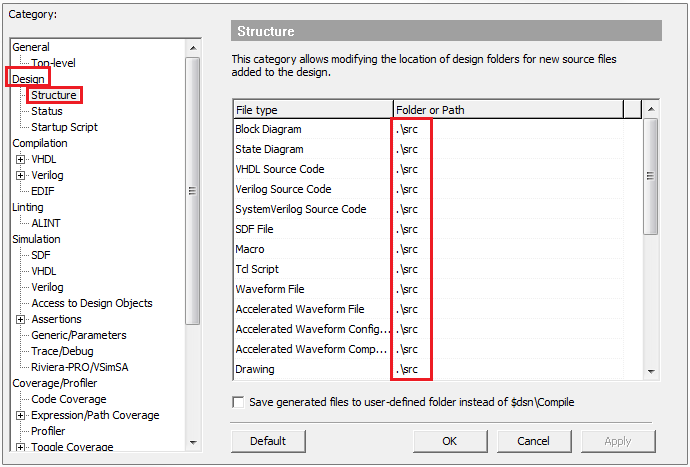

デフォルトでは Active-HDL は、図 1 に示すように固定のディレクトリ構造をもち、全てのデザインファイルは /src フォルダに、ブロック図やステートマシンから生成される HDL ファイルは /compile フォルダに保存します。デザインの構造は、Tools | Preferences | Design Structure にて設定できます。

図 1 デフォルトのディレクトリ構造

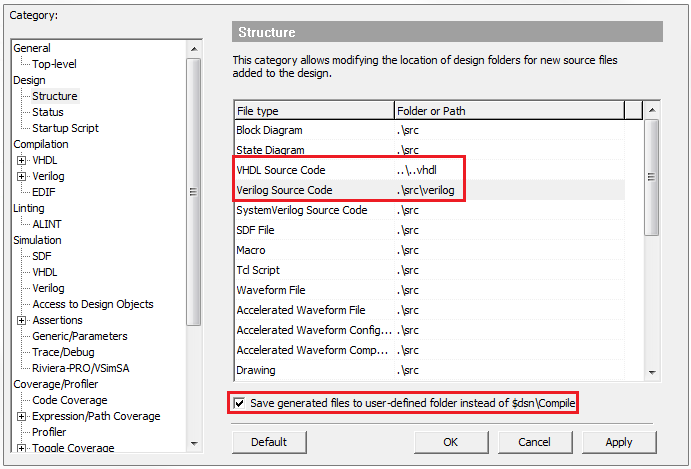

ユーザ定義のデザイン構造は次の手順で作成します。

-

各ファイルタイプの “Folder or Path” カラムをダブルクリックします。

-

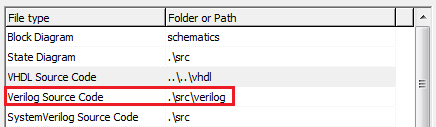

図2に示すように、ファイルを保存するディレクトリパスを定義します。

指定したフォルダが存在しないことを確認してください。Active-HDL は指定したフォルダを作成し、そこにファイルを保存します。ここでのディレクトリの指定は、定義済みの変数 $dsn で示すカレントデザインディレクトリを基準とした相対パスで行います。 $dsn 変数は Read-only です。

図 2 ユーザ定義のディレクトリ構造

ユーザ定義のディレクトリ構造の設定

Let’s take a closer looks at each individual setting above in Figure 2 to learn how user-defined directory structure works.

ディレクトリの作成

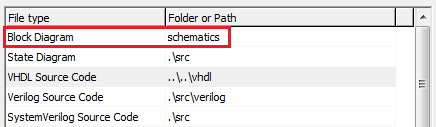

下図3で示す設定では、ブロック図のファイルを $dsn/schematics フォルダに保存します。例えばデザインディレクトリが C:\My_Designs\fifo の場合、ブロック図ファイル .bde は C:/My_Designs/fifo/schematics に保存されます。

図 3 ディレクトリの作成

ディレクトリパスの設定

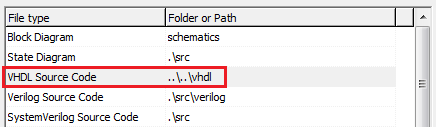

下図4で示す設定では、$dsn から2階層上に vhdl フォルダを作成し、VHDL ソースファイルを C:/vhdl に保存します。

図 4 ディレクトリパスの設定例1

下図5で示す設定では、$dsn/src ディレクトリの下に verilog フォルダを作成します。Verilog ソースファイルは、C:\My_designs\fifo\src\verilogに保存されます。

図 5 ディレクトリパスの設定例2

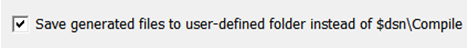

回路図から生成されるHDL ファイルの管理

下図6のオプションを選択すると、ブロック図やステートマシンから自動生成されたファイルは、コード生成ターゲットの言語に応じて VHDLまたは Verilog Source Code カテゴリで指定されたディレクトリに保存されます。本オプションをチェックしていない場合は、ブロック図やステートマシンから自動生成されたファイルは $dsn\compile フォルダに保存されます。

図 6 回路図から生成される HDLファイルの管理

ユーザ定義のディレクトリ構造へのファイルの保存

ディレクトリ構造を設定し Apply ボタンを押すと、下記のファイルは新しい設定に基づいて自動管理されます。下記の操作実行時に、ファイルは定義されたディレクトリに保存されます。

-

最初から新しいソースファイルを記述する、または New source File ウィザードを使って作成する時。

-

デザインにファイルを local copy として追加する時。

-

ブロック図やステートマシンから、または Code2Graphics 変換ウィザードにより HDL ソースファイルが生成される時。

-

サードパーティプロジェクトのファイルを Active-HDL にインポートする時。

ユーザ定義のディレクトリ構造を既存のデザインに適用する方法

9.1以前のバージョンで作成されたデザインの構造を更新するには、‘design’ または ‘workspace’ コマンドに –convertstructure オプションを付けてデザインを開きます。下記の例を参照してください。

design open –convertstructure

ディレクトリ構造は一旦変換されると、以前の状態に戻すことはできません。

注意: 9.1以前のバージョンで作成されたデザインをGUIで通常通り開く場合には、ユーザ定義のディレクトリ構造は自動では反映されません。

注意: 以前のバージョンのデザインにリンクしているファイルについては、ユーザ定義のデザイン構造は反映できません。それらのファイルは直接デザインに追加してください。

チームベースのデザイン構造の展開

デフォルトでは、Preferences | Design Structures の設定が $aldec\Dat\design_structure.cfg ファイルに保存されます。 $aldec は Active-HDL インストールディレクトリを指します。

-

design_structure.cfg ファイルは、編集したり共有することができ、ローカルなディレクトリにもサーバ等のネットワーク上にもコピー可能です。

-

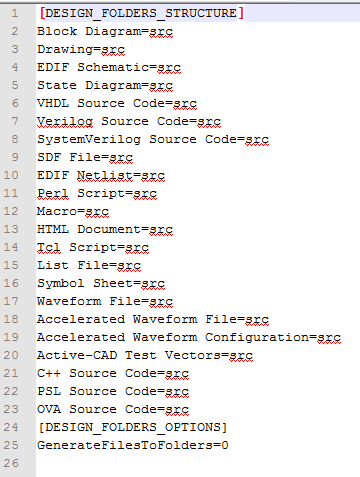

下図 7 は design_structure.cfg の内容を示しています。= の右側に表示されているディレクトリパスを編集することができます。パスは $dsn 変数からの相対パスで指定します。

図 7 design_structure.cfg ファイルの内容

-

design_structure.cfgファイルをサーバ等のネットワーク上にコピーすることができ、チームメンバーが同一ファイルを各自のActive-HDL環境で参照することにより、design_structure.cfgで定義されているデザイン構造を共有することができます。ローカル環境で参照するには、$activehdlteamhome変数を使ってdesign_structure.cfgファイルのコピーが保存がされているディレクトリを指します。

デフォルトでは$activehdlteamhome変数は設定されていません。 コンソールウィンドウにて ‘set’ コマンド を使って、$activehdlteamhome変数を指定します。

set activehdlteamhome \\hummer\hw\main_board\fpga\prj_settings

-

$activehdlteamhomehe変数が設定されると、GUI のPreferences | Design Structuresでの編集はできなくなります。デザイン構造を変更する場合には、変数が指すdesign_structure.cfgファイルを修正します。変数が指す設定ファイルを参照できない場合には、Active-HDLはツールのデフォルト設定である$aldec\dat\design_structure.cfgを参照します。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.