SystemVerilog のコンパイル用ソースコード解析の設定

はじめに

HDLエディターは、コンパイルプロセスを始める前にVHDLあるいはVerilog/SystemVerilogソース・コードを確認することが可能です。HDLコードを開発時にバックグラウンドで実行されるソース・コード解析は、新しく作成されたソース・コードにエラーがないか、修正を必要とするかどうかを確認することを可能にする事前情報を提供します。

コード解析を使用する方法

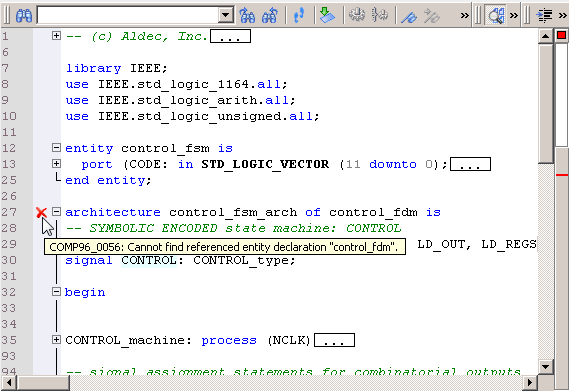

ソースコードの新しい行の入力を開始するたび、またはコードのブロックを張り付けた際(例えば、クリップボードにコピーしたり、コードの自動補完機能を使用して挿入)に解析が自動的に実行されます。ソースコードのブロックの記述完了後構文が正しい場合は、アウトラインウィンドウにそのブロックに関する新しい項目が表示されます。逆に構文やコードの整合性の問題がHDL ファイルで検出された場合には、HDL エディタウィンドウ上でエラーマーカーが表示されます。誤ったコードのラインあるいは不完全な部分は、図1に示されるようなHDLエディタウィンドウの左側余白上の赤いマーカーによって指示されます。

図1

エラーマーカーの上にマウス・ポインタを置くと、ツールチップが表示されます。それはエラーID を表示し、ショートエラーメッセージでソースコードの潜在的な問題についての確認/修正する内容を示します。

SystemVerilog デザインでの使用

SystemVerilog デザインでは、ファイル内で使用されるファンクションおよびクラスが現在の作業ディレクトリ外にある `include ファイルで定義されているため、ソースコード解析で”誤って”エラーマーカーをいくつかの行に表示することがあります。外部ファイルをインクルードするデザインに対しては、作業環境を適切に構成する必要があります。インクルードを多用するUVMデザインでは、これは典型的です。

ワークスペースに基づくアプローチ

ワークスペース/デザインを開いている場合、下記のオプションのうちのいずれかに従うことでHDLエディター内の不要なエラーマーカーを削除できます:

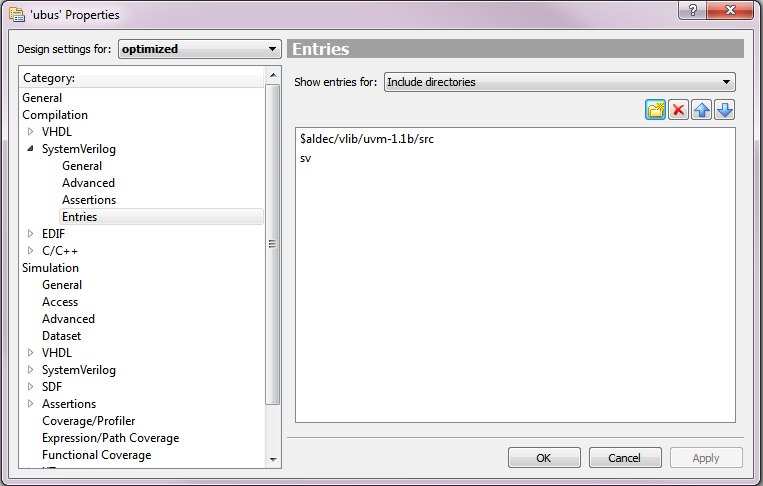

オプション1:デザインプロパティのSystemVerilog entries でインクルードファイルを追加

デザイン名を右クリックし、Properties を選択。プロパティダイアグラムボックスで、Compilation | SystemVerilog | Entries に進む。ここで、図2のようにインクルードファイルを含んでいるディレクトリを追加します。

図2

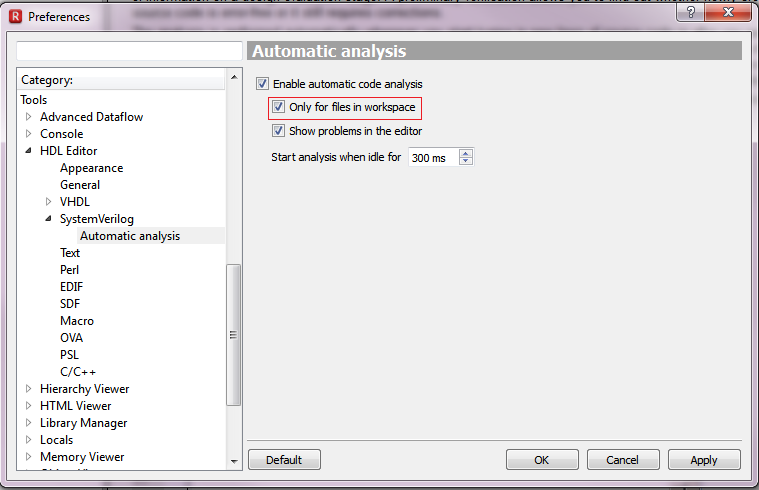

NOTE: Riviera-PROで開いた他ファイルで使用せずにワークスペース内のソースファイルにだけソースコード解析を使用したい場合、あなたはグローバルプリファレンス・ダイアログボックスで次オプションを有効にすることが可能です。

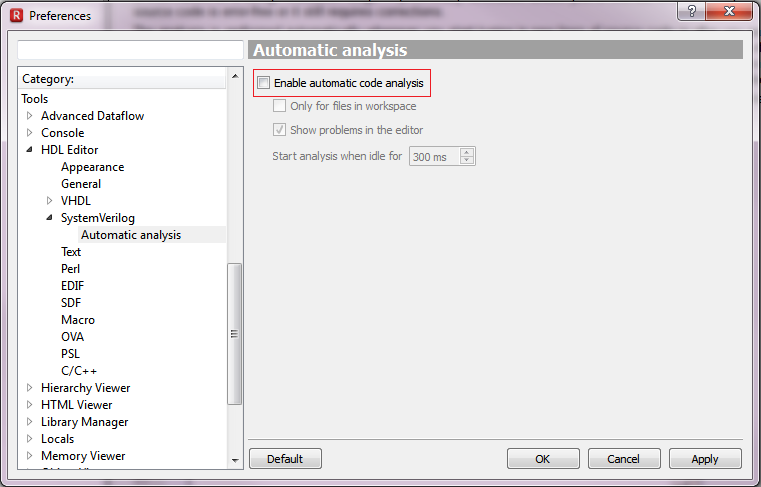

Tools | Preferences | Tools | HDL Editor | {VHDL | SystemVerilog}) に移動し、ここで図3のように Only for files in workspace をチェック。

図3

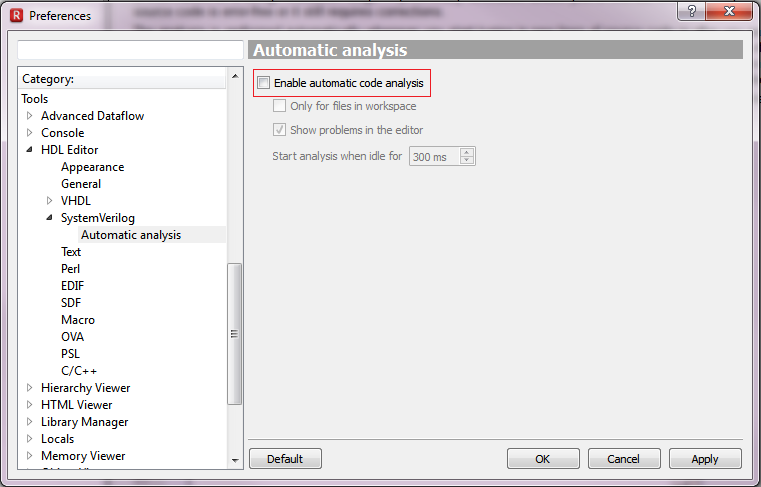

図4

オプション2: ソースコード解析の完全無効化

もしソースコード解析を完全に無効にしたい場合、Tools | Preferences | Tools | HDL Editor | {VHDL | SystemVerilog}) に移動し、ここで図4のようにEnable automatic code analysis のチェックを外します。

ファイルブラウザベースのアプローチ

ワークスペース/デザインを持たずスクリプトを使用してツールを実行している場合、”不完全な”赤いマーカーを取り外すために以下のオプションが使用できます。

オプション1:グローバルプリファレンス・ダイアログボックス内のSystemVerilog entiries にインクルードファイルを追加

Tools | Preferences | Compilation | SystemVerilog | Entries に移動し、ここで、図5のようにインクルードファイルを含んでいるディレクトリを追加します。

図5

オプション2: ソースコード解析の完全無効化

もしソースコード解析を完全に無効にしたい場合、Tools | Preferences | Tools | HDL Editor | {VHDL | SystemVerilog}) に移動し、ここで図4のようにEnable automatic code analysis のチェックを外します。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.