ALINT-PROでブロックレベルデザイン制約

はじめに

このアプリケーションノートでは、ブロックレベルの制約を使用して、ベンダー固有のプリミティブ、アナログ実装のブロック、およびブラックボックスとして処理されたIPコアを表すビヘイビアの合成不可能なデザインセルを記述して、ALINT-PROによる高品質のリンティング結果を提供する方法を示します。

本ドキュメント内で使用されるサンプルソースコードは、ここからダウンロード出来ます。ファイルは複数プロジェクトを持つ単一ワークスペースが含まれています。ADC_componentsプロジェクトは、制約と合わせてこの記事で使用する全てのコンポーネントが含まれています。他のプロジェクトは全てADC_componentsプロジェクト関連し、そこから使用されるコンポーネントになります。ワークスペースからプトジェクトは、これらのコマンドの後半で参照されます。

ブロックレベルデザイン制約

ブロックレベルデザイン制約は、デザインユニットの種々の特性を記述するために使用可能なコンソールコマンドのセットになります。この種類の記述はHDL記述を上書きし、HDLコードから情報を抽出することが出来な場合にツーツに追加情報を与えるために使用されます。制約コマンドは、暗号化されたIPモジュール、合成不可およびビヘビア記述、ブラックボックス、およびカスタム同期セルを記述するために使用されます。ブロックレベルのデザイン制約は現在のライブラリのデザインユニットに適用され、アタッチライブラリ、グローバルライブラリまたは他プロジェクトのプロジェクトライブラリの内容を変更することはできません。制約コマンドは*.adcファイルで指定され、正規のソースとしてプロジェクトに追加する必要があります。ブロックレベル制約は、次の2グループに分けることができま:

-

ブロックレベルゲッター - コマンドはライブラリセルまたはピンに関する情報を取得するために使用されます。これには、get_libs, get_lib_pins, get_lib_cells, get_lib_cell_paths, and report_attributesが含まれます。

-

ブロックレベルセッター - コマンドはデザインユニットの特性を指定するために使用されます。これには、set_cell, set_pin, create_cell_clock, create_generated_cell_clock, set_input_cell_delay, set_output_cell_delayが含まれます。

ポートとセルの役割

ブロックレベル制約内で最も一般的な使用法は、指定されたセルのセルとピンの役割を指定することです。セルの役割は、全体のセルを分析し

異なるアルゴリズムで使用されます。たとえば、ステートをトップレベルのフリップフロップにインスタンスしないチェッカは、チェックを実行するセルタイプを参照します。

役割はset_cellコマンドを使用して指定することができます:

set_cell [-kind <cell_kind>] [-function <lib_function>] <lib_cells_pattern>

[-if <boolean_condition>] [-f <list_file>]

コマンドはセルの役割を定義する-kind <cell_kind>引数を受け付け、get_lib_cells

ADC_componetsライブラリのIBUFセルについて考えてみましょう:

entity IBUF is port ( data_in: in std_logic_vector(7 downto 0); data_out: out std_logic_vector(7 downto 0) ); end entity IBUF;

inout_pad ロールを割り当てるには、次のset_cellコマンドを使用します:

set_cell -kind inout_pad [get_lib_cells ADC_components/IBUF]

さて、このセルは、デザインでインスタンシエートされていれば、リンティング中にALINT-PROエンジンによって入力パッドとして正しく認識されます。

-kind 引数には、フリップフロップ、ラッチ、マルチプレクサなどのさまざまなセルタイプを使用できます。 しかし、セルタイプのみを指定するだけでは、解析中にそのようなコンポーネントを適切に処理することはできません。これは、セルのピンとそのピン間のタイミング依存性を明示的に宣言することが重要なためです。

ADC_componetsライブラリに存在するフリップフロップを記述で説明します:

entity FF is port ( clk: in std_logic; rst: in std_logic; data: in std_logic; Q: out std_logic );

最初にset_cellコマンドでflip-flopの役割を割り当てましょう:

set_cell -kind flip-flop [get_lib_cells ADC_components/FF]

現在、セルのすべてのピンを記述する必要があります。これはset_pinコマンドを使用して行うことができます:

set_pin [-kind <pin_kind>] [-function <lib_function>] [-polarity <signal_polarity> | -level <signal_level>]

<lib_pins_pattern> [-if <boolean_condition>] [-f <list_file>]

このコマンドはセルの種類を指定する-kind 引数、-polarity(制御信号の極性を指定するために使用されます)オプションおよび-level(使用されているいくつかの出力端子は常に値で駆動されている場合)引数を受け付けます。コマンドは、それによって動作するピンを定義するget_lib_pins (<lib_pins_pattern>)コマンドの出力を受け付けます。フリップフロップのために次の制約を作成します:

set_pin -kind async-reset -polarity active-high [get_lib_pins ADC_components/FF/rst] set_pin -kind input [get_lib_pins ADC_components/FF/data] set_pin -kind output [get_lib_pins ADC_components/FF/Q]

これらのコマンドはclkピンを除く、フリップフロップのすべてのピンを記載しました。クロックピンを記載するには、create_cell_clock制約が使用する必要があります:

create_cell_clock [-edge <signal_edge>] [-name <clock_name>] <source_objects>

[-if <boolean_condition>] [-f <list_file>]

コマンドは、-edge(立上りまたは立下りのクロックエッジを指定できます)、-name(クロック名の指定、create_generated_cell_clockコマンドからの参照結果を使用することができます)、およびget_lib_pins制約の出力(クロックピンの定義)を受け付けます:

create_cell_clock -edge rising [get_lib_pins ADC_components/FF/clk]

ここまでカスタムフリップフロップについて記載を行いました。リンティング中、デザインと合わせて使用するとALINT-PROエンジンによって適切に認識されます。

コンポーネントの詳細は、"ADC_components"プロジェクトを参照してください。

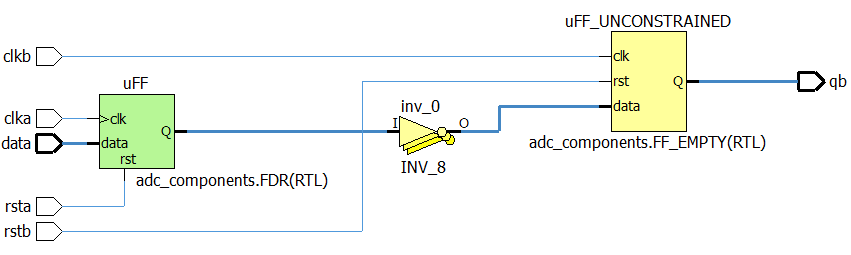

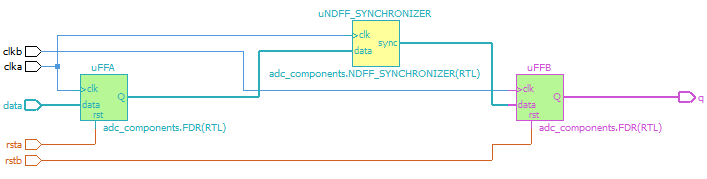

図 1 制約されたエレメント

単一のコマンドを使用して、最も単純なセル(フリップフロップ、マルチプレクサ、組み合わせゲートなど)のいくつかを記述するための簡略化された構文があります。簡略化は、特定ライブラリセルの入力ピンの表現を形成するために使用する「ライブラリ関数」と呼ばれる特殊な高レベルのブロックレベル制約コマンドを使用して実現できます。ライブラリ関数は、-function引数を使用してセル内の対応する出力ピンに関連付けられます。このように指定された入力ピンと出力ピンの関係は、クロックゲーティングスキームやDFTチェックなどの検出時に組み合わせパスを適切に処理できるため、より正確な設計解析結果を提供します。また、セルタイプはライブラリ関数から導き出すこともできます。単純なセルの場合、ライブラリ関数がツールに多くの情報を提供するため好ましい記述スタイルになります。

フリップフロップの説明では、以前のバージョンの代わりに次の制約を使用できます。

これは特定のライブラリセルの入力ピンの表現を形成するために使用される。

ライブラリ関数は、-function引数を使用して、セルの対応する出力ピンに関連付けられます。 このように指定された入力ピンと出力ピンの関係は、クロックゲーティングスキームやDFTチェックなどの検出時に組み合わせパスを適切に処理できるため、より正確な設計解析結果を提供します。また、セルタイプはライブラリ関数から導き出すことができます。単純なセルの場合、ライブラリ関数がツールに多くの情報を提供するため、これは好ましい記述スタイルです。

私たちのフリップフロップの説明では、以前のバージョンの代わりに次の制約を使用できます。

set_pin -kind output -function [lib_dff \ -in [get_lib_pins ADC_components/FDR/data] \ -clr [get_lib_pins ADC_components/FDR/rst] \ -clock [get_lib_pins ADC_components/FDR/clk]] \ [get_lib_pins ADC_components/FDR/Q]

すべての制御ピンは、このように記述されるとき、アクティブ”H"の極性を得ます。クロックピンを立ち下がりエッジに切り替えるには、クロックピンのためにcreate_cell_clockコマンド、-function引数を指定してset_pin制約に追加して呼び出す必要があります。

それでは、これらのコンポーネントを使用するプロジェクトを解析してみましょう。"ADC_constrained_elements"には、2つのセルが含まれています:適切に制約されているFDRと制約されていないFF_EMPTYデータは他1セルから送信されており、異なるクロックがセルに適用されています。次の操作で解析を実行します:

-

“ADC_constrained_elements”プロジェクトの実行 - ADC_constrained_elementsノード上のプロジェクトマネージャのポップアップメニューからRunボタンをクリック(ADC_componentsライブラリプロジェクトは、ADC_constrained_elementsに関連付けを設定すると、最初に実行されます)

-

スケマティックビューワを開く - ADC_constrained_elementsノード上のプロジェクトマネージャのポップアップメニューからShow Schematicボタンをクリック

上記のアクションは、スキーム表示にスケマティックビューアをもたらします(図 1)。見易いように、入力した制約はスケマティックビューアのコンポーネント表現に影響を与えます - FDRコンポーネントのuFFインスタンスはフリップフロップとして表示されます。そしてFF_EMPTYセルは内部接続をせずに空として表示されます。バイオレーションビューア(バイオレーションビューアの表示は、メインメニューでView | Linting Windows | Violation Viewerボタンをクリックするか、Alt+7ショートカットを使用)に移動した場合、“ADC_constrained_elements”プロジェクトで違反が検出されないことが分かります(図 2)。

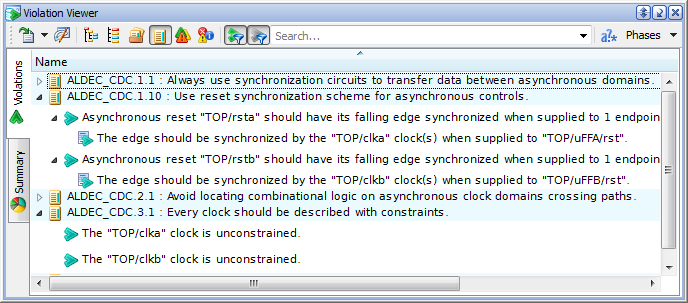

図 2 "ADC_constrained_elements"プロジェクトのバイオレーション検出

非同期クロックドメイン間のクロッシングで違反を受信するには、制約を2番目のセルにも追加する必要があります。ワークスペースに“ADC_crossings”プロジェクトがあります。これは"ADC_constrained_elements"プロジェクトと同じ構造になっていますが、2段目のセルに制約を違っています。

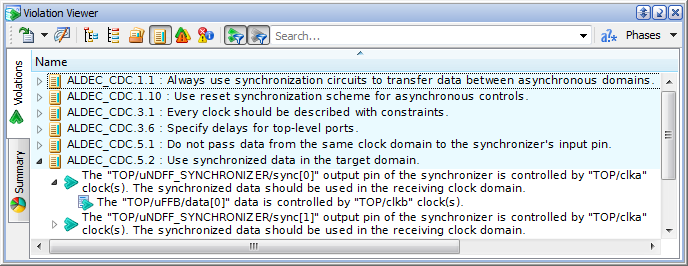

"ADC_crossings"プロジェクトの解析を実行しバイオレーションビューアを開いた場合、クロックドメイン間のクロッシングで同期化不良の違反があることが分かります(図 3)。新しいCDCパスが検出され非同期として報告されるだけでなく、クロック抽出アルゴリズムがuFFBフリップフロップを考慮し別の有効なクロックエンドポイントを得ることが出来るため、自動的に検出されたクロック数が増加しました(ルールALDEC_CDC.3.1違反)。また、ALDEC_CDC.1.10の違反は、異なるドメインからのフリップフロップの2つの制御ピンへのアサート解除の同期が無く、非同期リセットが接続されていることを示しています。

図 3 適切に制約を付与したセルで違反を報告

クロック生成

デザイン制約のための別用途として、クロックジェネレータの記述があります。マスタークロックと呼ばれるクロックを受け入れるセル、および出力としてジェネレートクロックと呼ばれる別クロックの生成を行います。この出力クロックを制限するには、create_generated_cell_clock コマンドを使用する必要があります:

create_generated_cell_clock -source <master_source> | -master_clock <cell_clock_name> [-divide_by <divide_by>]

[-multiply_by <multiply_by>] [-phase_shift <phase_shift>] [-name <name>] [-invert]

[-combinational] <source_objects> [-if <boolean_condition>] [-f <list_file>]

コマンドには、マスタクロックピンまたはマスタクロック名を指定する-sourceと-master_clock引数を受けつけます。-multiply_byと-divide_by引数は生成されたクロックの周波数の変更設定が可能、-invert引数は逆位相クロックを定義、そして-combinational引数はマスタクロックと同じ周波数/位相のクロックを定義、-phase_shift引数はマスタと生成されたクロック間の位相差を指定、そして-name引数はクロックジェネレータを持っていると仮定します。

下記クロックジェネレータを使用していると仮定しましょう:

entity CLK_GEN is generic ( DIVA : integer := 2; DIVB : integer := 2 ); port ( CLK: in std_logic; CLK_OUT: out std_logic; CLK_OUT_DIVA: out std_logic; CLK_OUT_DIVB: out std_logic ); end entity CLK_GEN;このコンポーネントは、入力クロック1つと生成クロック3つを持っており、生成クロックの周波数を定義するgeneric 値があります。

最初にセルの役割を定義する必要があります。今回のケースはクロックジェネレータであるため、set_cellコマンドで行うことが可能です:

set_cell -kind clock_generator [get_lib_cells ADC_components/CLK_GEN]

次に入力クロックを定義する必要があります。create_cell_clockコマンドを使用して、それを行うことが出来ます:

create_cell_clock -edge falling [get_lib_pins ADC_components/CLK_GEN/CLK]

メインクロックを定義すると、生成クロックの作成に進む事が出来ます。最初のクロック出力(CLK_OUT)は、クロックと同じ周波数で、このようなクロックを定義するには-combinational引数を使用する必要があります:

create_generated_cell_clock -combinational -source [get_lib_pins ADC_components/CLK_GEN/CLK]

[get_lib_pins ADC_components/CLK_GEN/CLK_OUT]

ここでは、-source 引数でマスタクロックピンと、引数を使用しない値による生成クロックピンの指定を行います。残りの2クロックの実際の周波数は、generic 値に依存します。この様なクロックを定義するために、-divide_by引数の値として式を指定する必要があります。式は通常のTCL 構文に従い、中括弧('{'と'}'の文字)で記述されます。一般的な変数は、先頭にドル記号をつけた名前で参照できます。この例での式は簡単です - generic 値自体は、以下のような記述を使用します:

create_generated_cell_clock -divide_by {$DIVA} -source [get_lib_pins ADC_components/CLK_GEN/CLK] \

[get_lib_pins ADC_components/CLK_GEN/CLK_OUT_DIVA]

create_generated_cell_clock -divide_by {$DIVB} -source [get_lib_pins ADC_components/CLK_GEN/CLK] \

[get_lib_pins ADC_components/CLK_GEN/CLK_OUT_DIVB]

上記の制約は、適切なリンティングを実行するためのクロックジェネレータセルを記述するのに十分です。

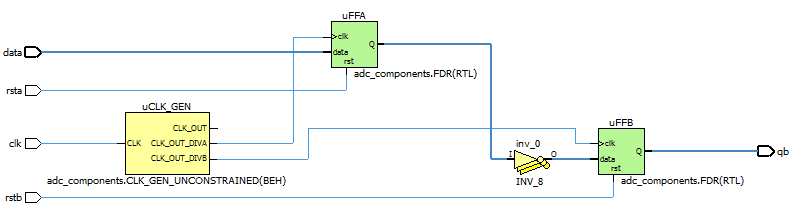

ワークスペース内に"ADC_generator_unconstrained"プロジェクトがあります。このプロジェクトは、2つのフリップフロップを駆動する異なるクロックを持ったクロックジェネレータセルを含みます。(図 4)

図 4 未制約のクロックジェネレータセル

ALINT-PROは自動的にデザインで使用されるクロックとリセットを検出します。検出されたクロックは、下記手順で表示出来ます:

-

アクティブプロジェクトとして“ADC_generator_unconstrained”プリジェクトを設定 - ADC_generator_unconstrainedノード上でプロジェクトマネージャのポップアップメニューからSet Project as Activeボタンをクリック

- “ADC_generator_unconstrained”プロジェクトを実行 - ADC_generator_unconstrainedノード上でプロジェクトマネージャのポップアップメニューからRunボタンをクリック(ADC_componentsライブラリプロジェクトは、ADC_constrained_elementsに関連付けを設定すると、最初に実行されます)

-

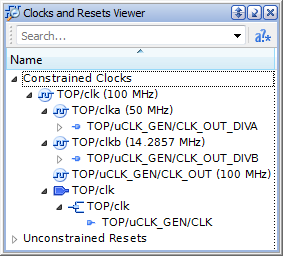

Clocks and Resets Viewerを開く - メインメニューからView | Design Management Windows | Clocks and Resets Viewerボタンをクリックするか、Alt+5ショートカット

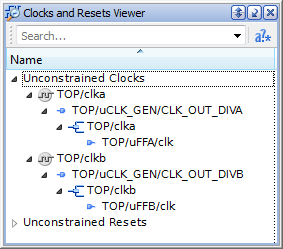

Clocks and Resets Viewerで、ALINT-PRO が検出した2つのクロックが確認できます(図 5)。検出されたクロックツリーは理想的ではありません:最初はクロックは個々のクロックとして検出、次にTOP/clkポートはクロックとして検出されません。

図 5 未制約のクロックジェネレータがあるクロックを検出

自動検出の結果を改善するために、クロックジェネレータセルの制約を指定する必要があります。“ADC_generator”プロジェクトがあり、同じ構造を持っている“ADC_generator_unconstrained”プロジェクトとの唯一の違い - クロックジェネレータセルは制約と一緒に記述している。解析を実行しClocks and Resets Viewerを開いた場合は、さらに3クロックが検出された事が判ります(図 6)。マスタークロック(TOP/clk)と2つの生成クロック(TOP/uCLK_GEN/CLK_OUT_DIVAと TOP/uCLK_GEN/CLK_OUT_DIVB)。そして、正しく3クロックが検出され、正しいリンティング結果が得られた事が判ります。

図 6 制約済みクロックジェネレータとクロック検出

検出したクロックは、save_constraintsコマンドを使用して*.adcファイルに保存することが可能です。コマンドは“ADC_generator”プロジェクトに付けられたmain.adcに制約を保存します(main.sdc は、プロジェクト設定のSave constraints toオプションで指定されています)。制約保存後、クロックに対して下記レコードが生成されます:

create_clock -period 10 -name TOP/clk [ get_ports TOP/clk ] create_generated_clock -source [ get_ports TOP/clk ] -combinational -name TOP/uCLK_GEN/CLK_OUT [ get_pins TOP/uCLK_GEN/CLK_OUT ] create_generated_clock -source [ get_ports TOP/clk ] -divide_by 2 -name TOP/clka [ get_pins TOP/uCLK_GEN/CLK_OUT_DIVA ] create_generated_clock -source [ get_ports TOP/clk ] -divide_by 7 -name TOP/clkb [ get_pins TOP/uCLK_GEN/CLK_OUT_DIVB ]

そこで、HDLコードで供給される一般的な値はエンジンによって認識され、生成クロックの記述に挿入されていることを確認できます。

マルチクロックを使用するセルの記述

例えばデュアルポートRAMセルの様に単一セルでマルチクロックを受信し、そのピンが異なるクロックに依存する事が可能です。このような状況を処理するには、set_input_cell_delayとset_output_cell_delay制約があります:

set_input_cell_delay -clock <cell_clock_name> -reference_pin <lib_pin> [-add_delay] <objects>

[-if <boolean_condition>] [-f <list_file>]

set_output_cell_delay -clock <cell_clock_name> -reference_pin <lib_pin> [-add_delay] <objects>

[-if <boolean_condition>] [-f <list_file>]

これらの制約は、クロック名(-clock引数)またはクロック・ピン名(-reference_pin引数)、get_lib_cellsコマンド(<objects>)出力を受け入れます。一度コマンドを実行すると、これらのピンは指定したクロックでサンプル/ドライブされていることえおALINT-PROエンジンに通知します。

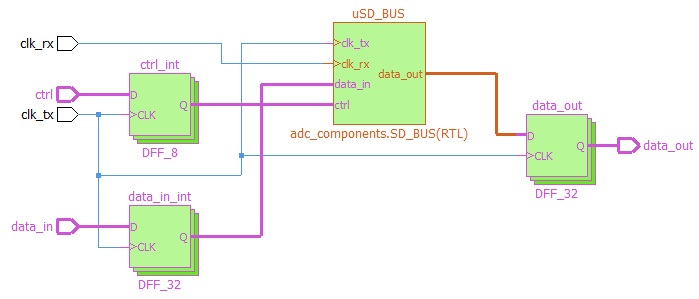

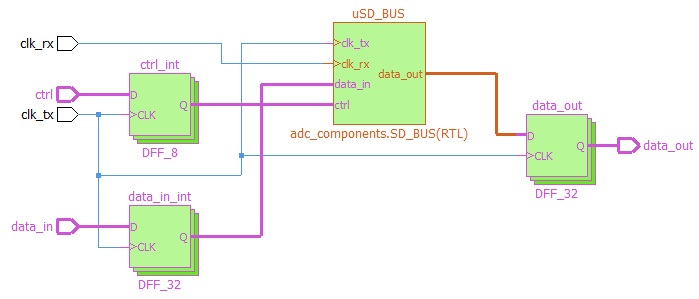

シンプルなデュアルクロックバスを考えてみましょう:

entity SD_BUS is port ( clk_tx : in std_logic; clk_rx : in std_logic; data_in : in std_logic_vector(31 downto 0); ctrl : in std_logic_vector(7 downto 0); data_out : out std_logic_vector(31 downto 0) ); end entity SD_BUS;

すべてのピンは、上記のようにcreate_cell_clockおよびset_pin制約で記述する必要があります。さらに、set_input_cell_delay / set_output_cell_delay制約は、セルのクロックピン以外のピンごとに指定する必要があります。制約は次のようになります。

# Bus Inputs set_input_cell_delay -reference_pin [get_lib_pins ADC_components/SD_BUS/clk_tx] [get_lib_pins ADC_components/SD_BUS/data_in] set_input_cell_delay -reference_pin [get_lib_pins ADC_components/SD_BUS/clk_tx] [get_lib_pins ADC_components/SD_BUS/ctrl] # Bus Output set_output_cell_delay -reference_pin [get_lib_pins ADC_components/SD_BUS/clk_rx] [get_lib_pins ADC_components/SD_BUS/data_out]

このような制約がセルに定義され、ピンに接続されたデータとピン自体が異なるクロックによって制御されると違反が報告されます。ADC_busプロジェクトを実行すると、そのようなセルで報告された違反を調べることができます。このプロジェクトには、入力と出力がフリップフロップによってドライブされるSD_RAMインスタンスが含まれていますが、そのうちの1つは間違ったクロックで制御されます(図7)。

図 7. 検出されたCDCパスは、適切に制約されたデュアルクロックバスから始まります

RAMや非同期FIFOなど、頻繁に発生するデュアルクロックコンポーネント用の特別なショートカットがあります。ユーザーの便宜のために、次のライブラリ関数lib_ramとlib_async_fifoが用意されています。これらのライブラリ関数は、set_cellコマンドの-function引数の式として使用する必要があります。この場合、セルタイプだけでなく、クロックと他のI / Oとの間の依存関係も導き出すことができ、set_input_cell_delayおよびset_output_cell_delay制約を指定する必要はありません。

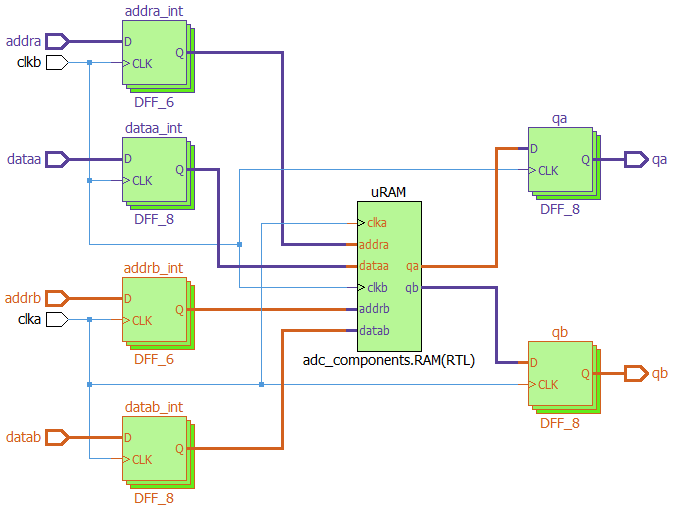

RAMセルで見てみましょう:

entity RAM is port ( clka : in std_logic; addra : in std_logic_vector(5 downto 0); dataa : in std_logic_vector(7 downto 0); qa : out std_logic_vector(7 downto 0); clkb : in std_logic; addrb : in std_logic_vector(5 downto 0); datab : in std_logic_vector(7 downto 0); qb : out std_logic_vector(7 downto 0) ); end entity RAM;

RAMの書き込みおよび読み取りインタフェースは、lib_interfaceライブラリ関数を使用して個別に記述する必要があります。 インタフェースのクロックポート以外の全てのポートはインタフェースクロックに依存するように設定されています。

set_cell -function [lib_ram \

[lib_interface \

-clock [get_lib_pins ADC_components/RAM/clka] \

-in [get_lib_pins ADC_components/RAM/dataa] \

-addr [get_lib_pins ADC_components/RAM/addra] \

-out [get_lib_pins ADC_components/RAM/qa]] \

[lib_interface \

-clock [get_lib_pins ADC_components/RAM/clkb] \

-in [get_lib_pins ADC_components/RAM/datab] \

-addr [get_lib_pins ADC_components/RAM/addrb] \

-out [get_lib_pins ADC_components/RAM/qb]]] \

[get_lib_cells ADC_components/RAM]

ADC_RAMプロジェクトには、すべての入力と出力がフリップフロップによってドライブされ誤ったクロックドメインによって制御されるRAMインスタンスが含まれています(図8)。 プロジェクトを実行して、報告された違反を調べます。

図 8. 検出されたCDCパスは、適切に制約されたRAMセルで開始および終了します

Genericに依存した制約

いくつかのデザイン制約が、あるgeneric値にのむ有効にすることは可能です。例えば特定のピンは、generic値に応じて非同期または同期リセットれることがあります。このような状況に対応するためには、-if引数を仕様する必要があります。この引数は、TCL 式ではパラメータとして取られます。generic値は、generic名の頭にドル文字'$'を付けて参照することが可能です。

次の例では、同期または非同期リセットがrstピンで推論されている場合、フリップフロップを制御するASYNC_RESETと言うgeneric値があります:

entity FF_GENERIC is generic ( ASYNC_RESET: boolean := true ); port ( clk: in std_logic; rst: in std_logic; data: in std_logic_vector(7 downto 0); Q: out std_logic_vector(7 downto 0) ); end entity FF_GENERIC;

そのようなモジュールを記述するため、rstピンのために2つの制約を必要とします:

set_pin -kind async-reset -polarity active-low [get_lib_pins ADC_components/FF_GENERIC/rst] \

-if {$ASYNC_RESET == true}

set_pin -kind sync-reset -polarity active-low [get_lib_pins ADC_components/FF_GENERIC/rst] \

-if {$ASYNC_RESET == false}

ここで、rstピンを非同期ピンと同期ピンとして定義する制約があります。しかし、これらの制約には、-if引数でしていた別の式を持っています。式の評価が真になる場合だけ対応する制約は適用され、これらの制約の1つだけが特定のセルに当てられます。

“ADC_generic_dependent”プロジェクトには、適用するgeneric 値を持ったFF_GENERICセルの2つのインスタンスが含まれています。このプロジェクトのための回路図がを図 9に示されています。ここで確認できる通り、uFF_ARSTは非同期リセットピン(rst ピンはセルの下部に表示)を持っており、uFF_SRSTセルは同期リセットピン(rstピンはセルの左側)を持っています。これはデザインリンティング時のチェッカーで検出されたバイオレーションに影響を与えます。

図 9 genericに依存した制約を持つセル

汎用/パラメータ値と同様に、ポートの定数値を条件式で使用することができます。定数ラインがデザイン内のセルのポートに接続されている場合、ポートの値は '0'、 '1'、 'X'、 'Z'のいずれかの文字で表されます。それ以外の場合、ポート値は ' - 'に等しくなります。 ポートの値は、ポートの種類に関係なく、常にバイナリ文字列を形成します(「0011」は小数点3に変換されません)。

generic/parameterとポート名、および式の誤り(誤った構文、ゼロ除算など)は、コマンド実行中の制約フェーズで検証されます。

カスタムシンクロナイザセルの記述

シンクロナイザセルの説明は、lib_synchronizerライブラリ関数を使用したset_cellコマンドに基づいています。カスタムシンクロナイザを作成するには、同期回路の記述を別のデザインユニットに配置する必要があります。簡単な2dff シンクロセルで見てみましょう:

entity NDFF_SYNCHRONIZER is port ( clk: in std_logic; data: in std_logic_vector(7 downto 0); sync: out std_logic_vector(7 downto 0) ); end entity NDFF_SYNCHRONIZER;

セルには次の制約を適用する必要があります:

set_cell -function [ lib_synchronizer \

-in [get_lib_pins ADC_components/NDFF_SYNCHRONIZER/data] \

-out [get_lib_pins ADC_components/NDFF_SYNCHRONIZER/sync] \

-read_clock [get_lib_pins ADC_components/NDFF_SYNCHRONIZER/clk] ] \

[get_lib_cells ADC_components/NDFF_SYNCHRONIZER]

ADC_synchronizerのプロジェクト制約で間違ってNDFF_SYNCHRONIZERセルが使用されました(図10)。

図 10. カスタムシンクロナイザ

uNDFF_SYNCHRONIZERシンクロナイザは、デザインに誤って配置されます。つまり、同じドメインからデータを受信し、同期化されたデータはターゲットドメインで使用されません。この結果、ALDEC_CDC.5.1およびALDEC_CDC.5.2チェッカからの違反が発生します。この内容は、バイオレーションビューア(図11)で確認できる可能性があります。

図 11. 誤って使用されたシンクロナイザの違反

制約によって割り当てられた値の確認

ブロックレベルの制約を作成する際の一般的なタスクは、特定のピンに適用される制約を検証することです。 ALINT-PRO にはreport_attributes TCLコマンドがあります。このコマンドはテキスト形式で供給されたオブジェクトの様々な特性を報告します。入力した様にブロック、チップレベルのゲッターの出力を受け入れます(例えば、get_clocks, get_resets, get_lib_pinsなど)。

例えば、上記の例からRAMセルのdataaピンに適用される制約を確認するため、次のコマンドを使用することが出来ます:

report_attributes [get_lib_pins ADC_components/SD_BUS/data_in]

属性とその値のセットを返します:

type: library pin name: ADC_components/SD_BUS/data_in kind: input direction: in sampled_by: clk_tx

ここで、このピンは通常のデータ入力ピン(kind: input)であり、clk_tx クロックピンで制御(sampled_by: clk_tx )されていることが確認出来ます。特定のピンの属性が明瞭な値の代わりにgeneric値に依存している場合、対応する式がコマンド出力として出力されます。

上記例のFF_GENERICコンポーネントのrstピンの属性について確認しましょう:

type: library pin name: ADC_components/FF_GENERIC/rst kind: ($ASYNC_RESET == false) ? sync-reset : ($ASYNC_RESET == true) ? async-reset : <unknown> direction: in polarity: ($ASYNC_RESET == false) ? active-low : ($ASYNC_RESET == true) ? active-low : <unknown>

ここで三項演算子は、種類と極性の属性のために構成されました。三項演算子は次の構造(<conditional_expression>) ? <true_condition> : <false_condition>を有し、互いを入れ子にすることができます。この式の条件式は、対応する制約コマンドの-if 引数の値として入力された式になります。

生成したクロックの属性をチェックする為に、次のゲッターを使用するべきです:get_lib_cell_paths。このコマンドは、開始点と終点のlibセルのピンの受入れ、およびデザイン制約によって導入されたピントの関係を返します。例えば、上記の例からCLK_GENセルの生成クロック CLK_OUT_DIVAの属性を確認したい場合、下記コマンドを使用することが出来ます:

report_attributes [get_lib_cell_paths -from ADC_components/CLK_GEN/CLK -to ADC_components/CLK_GEN/CLK_OUT_DIVA]

下記属性がレポートされます:

type: library cell path name: ADC_components/CLK_GEN/CLK:CLK_OUT_DIVA kind: cell_clock source_port: CLK destination_port: CLK_OUT_DIVA connection_kind: all-to-all divide_by: $DIVA inverted: false combinational: falseここでは、生成されたクロックのすべての特性の確認、およびgenericに依存したいくつかの値があれば対応する式で表示されます(例えば、divide_by: $DIVA)。

サマリ

ブロックレベルのデザイン制約は、任意の複雑なTCLフォーマットライブラリセルをク記述できる強力なメカニズムです。これには、特定のピンの役割(クロック、リセット、イネーブル、データなど)、ジェネレートクロックの生成、ピンとクロックの依存関係の指定も含まれます。また、特定のデザイン制約を指定することも可能です(genericで特定の値があるセルにのみ割り当てます)。制約作成プロセスを容易にするためにALINT-PROは、特定のピンに割り当てられている値を調べる事が可能なreport_attributesコンソールコマンドを提供しています。一度入力されたデザイン制約は、完全なルールセットを利用し正確なデザインリンティングを可能にし、プロジェクト内の合成不可能、およびビヘビア部分をプロダクトで利用可能にします。コマンド、引数、および関連するサンプルの詳細については、コマンドリファレンスドキュメント(ヘルプメニュー)を参照してください。

ALINT-PROは、同一の制約メカニズムを適用して、FPGAベンダのプリミティブを適切に処理します。ユーザーがベンダプリミティブを個々に記述することは想定されていませんが、デュアルポートRAMやマルチクロックFIFOのような複雑なプリミティブの場合、実際にはこれは非常にエラーが発生しやすい作業になる可能性があます。この制約は、最も頻繁に使用されるFPGAベンダーライブラリ(ザイリンクス、アルテラ、マイクロセミ)の製品に定義され、パッケージ化されています。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.