Riviera-PROを使用したUVVM入門

はじめに

UVVMとはUniversal VHDL Verification Methodologyの略になります。UVMとSystemVerilogは、ASICとFPGAの検証を可能にする最新の手法ですが、すべてのFPGAプロジェクトに対応できるものではありません。FPGAの開発にVHDLを使用しているほとんどの企業にとって、検証のためにUVMに変更することは意味がありません。そこで、VHDL専用にUVM/SystemVerilogが提供するすべての機能と利点を備えるUVVMが導入されました。さらに、VHDL Verification Components (VVC) と呼ばれる主要な改良が加えられています。

なぜUVVM?

VHDL2008では、言語自体が大幅に改善されました。オープンソースライブラリであるOSVVM (Open Source VHDL Verification Methodology) は、高度なランダム生成とファンクショナルカバレッジのサポートに優れています。これらの重要な機能を備えていますが、大規模デザインではデバッグが依然として最も重要であり、VHDL2008とOSVVMにはデバッグ機能が著しく不足しています。UVVMはこのギャップを埋めるものです。オープンソースでもあるBitvis Utilityライブラリは、ロギング/レポート、冗長性制御、アラート処理、および事前定義された値やイベントチェッカーなどを強力にサポートします。現在、Bitvis UVVM (Universal VHDL Verification Methodology) は、検証手法の中で最も重要な「検証コンポーネント」を提供します。UVVMユーティリティライブラリを使用した基本的なVHDLテストベンチには、次のものが含まれています:

-

ロギングと詳細度(verbosity)制御

UVVMが提供する利点の1つは、デザインやテストベンチを再コンパイルすることなく、シミュレーションメッセージ数を増減してシミュレーションを実行することができることです。UVVMメッセージでは、ユーザはプライオリティではなく詳細度を指定します。詳細度コントロールは、ユーザがコードをほとんど追加することなく、デザインやテストベンチを詳細に確認することに役立ちます。

たとえば、log(msg_id,msg[…]); は、そのmessage_idのverbosityが有効になっている場合のみ、特定のmessage_idのメッセージを表示します。

-

オプションのポジティブアクノリッジを含むアラートハンドリング

TこれもUVVMの機能の一つで、実行時に定義された階層ツリーに対する階層アラートレポートを提供します。アラートサマリーは、定義されたスコープのツリーとして表示されます。アラートカウンターは、ツリーをトップレベルに伝搬し、ユーザーに情報を提供するためユーザーは常に最新の情報を得ることができます。

たとえば、error(msg,[scope]); はシミュレーションがスコープに違反した場合、エラーメッセージを出力します。

-

簡略化されたランダム化

ランダム化は非常に重要です。データの特性を変えことで、DUTにランダムに刺激を与えることに他なりません。ランダム化によって、テストが困難なコーナーケースに到達することができます。UVVMでは、非常に簡単なコマンドを使用してランダム化を行うことができます。

たとえば、command v_int = random(min_value,max_value); これは、コマンドで指定された範囲の間の整数値を生成します。

-

BFMのサポートと例

BFMの例とサポートを理解し確認するために、まずBFMの定義を理解しましょう。BFMとは、Bus Functional Modelの略です。1つまたは複数の外部バスを持つ集積回路コンポーネントの合成不可能なソフトウェアモデルです。BFMは通常、ハードウェア記述言語のタスクとして定義され、複雑な波形やプロトコルを介してDUTに刺激を与えます。BFM は、シミュレーション用のテストベンチを作成するための再利用可能なビルディングブロックとしてよく使用されます。ここで、テスト対象のデザインの信号ポートは、シミュレーションの目的でテストベンチ内の適切なBFMに接続されます。トランザクションレベルモデルとも呼ばれます。このように、BFMに関連するサポートとサンプルもUVVMパッケージの一部として含まれています。

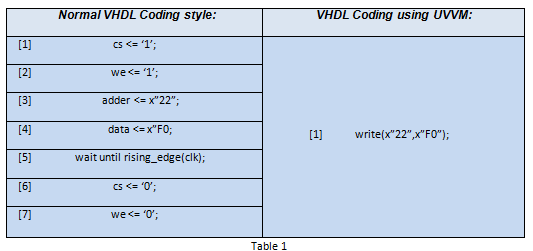

UVVMを使用してコーディングがどのように変化するかの基本的な考え方を、例を挙げて以下に説明します:

より高いレベルのトランザクション(例えば、リード、ライト、パケット送信、設定など)を処理することが容易になります。例えば、アドレス0x22のレジスタに0xF0を書き込む場合、通常のvhdlでは7ステップかかりますが、UVVMでは1ステップでそれを実現できます。以下の表1で、それを確認できます。

表 1

このように、UVMはシンプルなバスインタフェースを提供します。これとは別に、より大規模で複雑なデザインでは、より多くのインタフェース、インタフェース上のより多くの同時アクティビティ、値関連のコーナーケースとサイクル関連のコーナーケースが必要になります。これらのすべてのケースは、VVCをサポートしていないため、OSVVMだけでは達成できません。コーナーケースについて語る時は、検証を使用してそれらを見つけるためにより多くのロジックが必要になります。簡単にするために、次のような自由があればいいのですが::

-

構造化された方法で任意の数のインタフェースをコード化

-

モジュールテストベンチ間で主要なテストベンチ要素を再利用

-

擬似コードとほぼ同じくらい簡単にテストシーケンサをリード

-

テストシーケンサの検証仕様を認識

-

単一のテストシーケンサを見るだけで、イベントのシーケンスを理解可能

これらをすべて実現するために、UVVMはVHDL検証コンポーネント(VHDL Verification Component)と呼ばれる構造を提供します。これは何なのか、どのように役立つのか、気になりますよね!?では、それを見ていみましょう。

VHDL検証コンポーネントとは何ですか?

VVCは、UVVMと互換性がある特定のプロトコルインターフェースやロジック機能に対する自己完結型の検証ソリューションになります。これは手続き型であると同時に、トランザクションレベルのモデリングを提供します。VHDL検証コンポーネントは基本的にシーケンサからコマンドを受け取り、コマンドに応じてレシーバ側で実行するインターフェースとして機能します。VVCはVHDLエンティティ/コンポーネントで、複数スレッドや自律動作を可能としています。コマンドを介して制御可能であると同時に、カプセル化されています。したがって、テストベンチで公開されたくない重要な情報を隠すことに役立ちます。

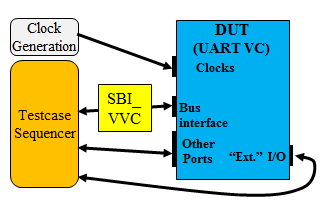

図 1 - ブロックダイヤグラムにおけるVVC

VVCを用いたシーケンサコマンド:sbi_write(SBI_VVCT,C_ADDR_TX,x”2A”); により、BFMがVVCからDUTに向かって実行されます。また、VVCでは、異なるインターフェイスのBFMを同時に実行することが可能です。具体的には、BFMプロシージャがブロッキングトランザクションであるのに対して、VVCはノンブロッキングトランザクションになります。また、VHDL検証コンポーネントとバスファンクションモデルの微妙な違いも理解することも重要です。VVCは基本的にCDM(Command Distribution Method)に従います。つまり、BFMは物理DUTに向かってすぐに実行されますが、CDMは常に実行可能なコマンドだけをVVCに分配して、そこで(多くの場合VVC内部のBFMを介して)すぐに、あるいは後で実行するために使用されます。したがって、CDMは物理DUTで信号を小刻みに動かすことはありません。

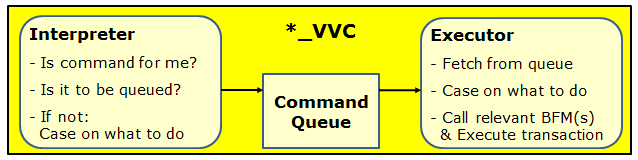

VHDL検証コンポーネントを使用した作業

VVCは3つのステージで構成されています。インタープリタ、コマンドキュー、エクゼキュータです。インタープリタは、シーケンサからコマンドを受け取るものになります。インタープリタは、シーケンサからコマンドを受け取ると、そのコマンドがキューに入れられるかどうかをチェックします。コマンドをキューに入れる場合は、第2ステージにコマンドキューが渡されます。コマンドキューステージからは、コマンドに関連するBFMを呼び出してトランザクションを実行するエグゼキュータステージに渡されます。このようなVVCの仕組みの最大の利点は、BFMの呼び出しを除くインタープリタとエクゼキュータの両方でコードの90%以上とその構造が同じままであるということです。

図 2 - VVCアーキテクチャ

Riviera-PROを使用してUVVMの使用を開始:

Riviera-PROでUVVMを使い始めるための最初のステップは、UVVMをダウンロードする必要があります。UVVMはBitvisのホームページからダウンロードすることができます。UVVMの最新バージョンをダウンロードするためのリンクは次のとおりです:http://bitvis.no/products/uvvm-vvc-framework/。最新バージョンのUVVMには、VVCフレームワークとユーティリティライブラリ、各種VHDL検証コンポーネント、UVVM-OSVVMサポート、テストベンチの概要と調整、その他多数が含まれています。下記はUVVMをダウンロードして正常に実行するために必要な正確な手順になります。

-

上記のリンクから、最新のUVVMをダウンロードしてください。

-

UVVMのウェブサイトからダウンロードしたファイルを解凍します。

-

Riviera-PRO -> Create a Workspace -> Create a Design を開き、ファイルをコンパイルします。

注:このドキュメントは、Riviera-PROでのUVVMの動作を反映しています。 Riviera-PROのライセンス/ダウンロード/機能の紹介が必要な場合は、次のリンクをクリックして詳細を確認してください:https://www.aldec.com/jp/products/functional_verification/riviera-pro

Riviera-PROの詳細については、以下をクリックしてください: https://www.aldec.com/jp/support/resources/documentation/articles?type=&products=2&category=1&sub_category=&submit=Browse

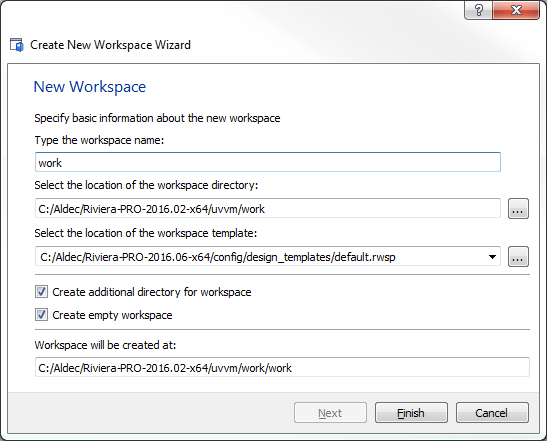

ワークスペースとデザインの作成

Riviera-PROでは、個々のデザインとそのリソースをワークスペースとしてグループ化することができます。ワークスペースでは、複数のデザインを同時に追加して作業することができます。

-

File | Newに移動し、Workspaceをクリックします。 新しいワークスペースウィザードが起動します。

-

ワークスペース名を入力し、プロジェクトを作成する場所を選択します。

-

完了したら、OKボタンをクリックします。

図 3 - 'work'という名前のワークスペースの作成

-

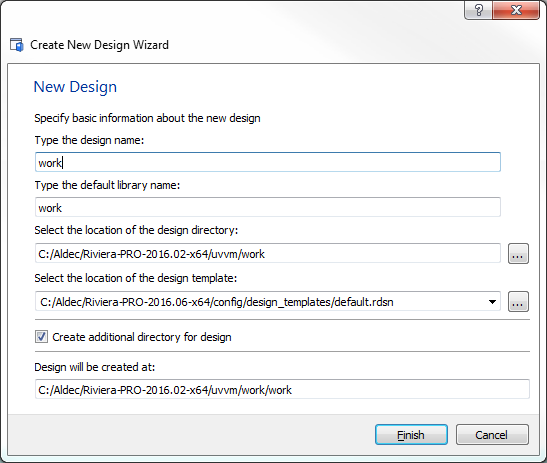

新しいワークスペースが作成されます。 次に、ワークスペースオプションを右クリックして、Add | New Designの順に移動します。 下記ウィンドウが表示されます。

図 4 - 'work'という名前のデザインの作成

-

完了したら、Finishボタンをクリックします。

-

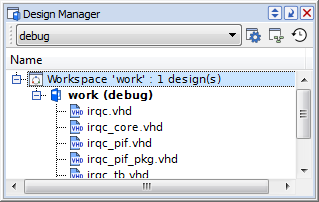

Design Managerに、ワークスペース名とそれに関連付けられた新しいデザインが表示されるようになりました。

図 5 - Design Manager

デザインへのファイル作成/追加

-

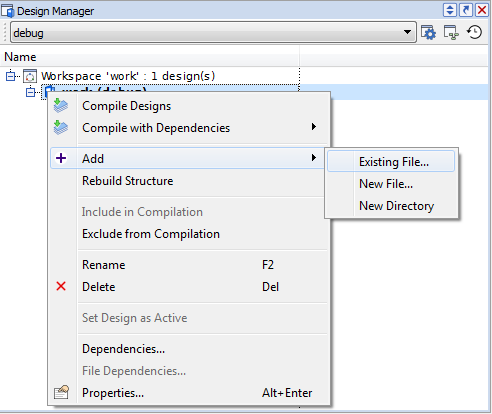

新規ファイル、既存ファイル、ディレクトリを作成するには、Design Managerウィンドウの任意の場所で右クリックし、Add | New fileをクリックします。

-

または、File | New メニューを使用して、新しいファイルを開き、デザインに保存することができます。

-

この例では、Bitvisによって提供された'bitvis_irqc'というサンプルを使用しています。これを開くには、Design Managerで右クリックし、Add -> Existing Fileと進み、ディレクトリをUVVMファイルをダウンロードした場所に変更し、現在のデザインに追加してくます。

図 6 - 新しいファイルの追加

-

すべてのデザインファイルとテストベンチを追加後、VVC_Frameworkのダウンロードの一部として提供されている必要なライブラリも必ず追加してください。これらのライブラリをRiviera-PROのライブラリ構成にアタッチしたら、古いバージョンのRiviera-PROでプリコンパイルされている可能性があるため、これらのライブラリをリフレッシュすることが重要です。

コンパイル

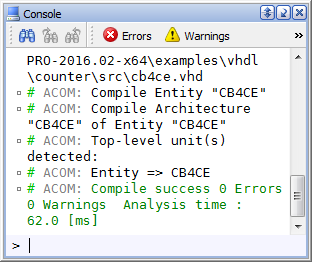

コンパイルはソースファイルを解析するプロセスです。ファイルに含まれる解析済みのデザインユニットは、シミュレータが理解できる形式でワーキングライブラリに配置されます。

ソースファイルのコンパイル

-

単一のファイルをコンパイルする場合は、Design ManagerのFilesに移動し、ファイルを右クリックし、ショートカットメニューからコンパイルを選択します。

-

あるデザインの Designタブを右クリックしてcompile allを選択すると、コンパイラは自動的にソースファイルの順序を変更し、デザインユニットのコンパイル順序が適切になるようにします。

図 7 - Console Windowのコンパイルメッセージ

イニシャルシミュレーション

必要なデザインユニットがすべて正常にコンパイルされたら、シミュレーションを初期化することができます。シミュレーションを初期化する前に、以下のことを確認してください:

-

トップレベルのデザインユニットが選択されていること。

-

トップレベルユニットが選択せずにシミュレーションを実行すると、シミュレータはユニットを選択するようダイアログボックスを表示します。

-

シミュレーションプロセスを開始するには、SimulationウィンドウからInitialize Simulationを選択する必要があります。このコマンドは、シミュレーションモデルのエラボレーションと初期化を開始します。エラボレーションでは、シミュレータはデザインユニットをロードし、コンピュータメモリにシミュレーションモデルを構築します。初期化中ではモデル内のすべてのオブジェクトが初期値を取得し、すべての平行プロセスが一時停止されるまで1回実行されます。

図 8 - イニシャルシミュレーション

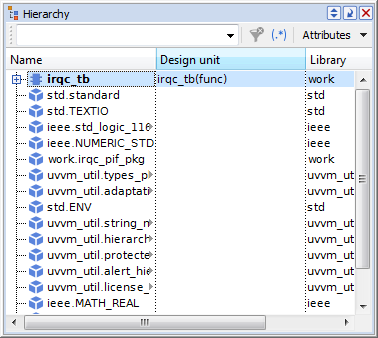

図 9 - Hierarchyウィンドウ

-

デバッグウィンドウを開き、テストベンチを最上位の階層として設定します。これを選択すると、Hierarchyウィンドウがポップアップ表示されます。

-

テストベンチモジュールを右クリックし、Add to | Waveforms オプションを選択します。waveformウィンドウがポップアップします。

-

Waveformウィンドウのオプションから実行オプションを選択することで、シミュレーションを実行することができます。

シミュレーションの停止/リスタート

-

シミュレーションセッションを終了するには、SimulationメニューからStop Simulationを選択します。

-

SimulationメニューからRestartオプションを選択すると、シミュレーションをリスタートできます。

図 10 - シミュレーションの停止/リスタート

Waveformビューワ

-

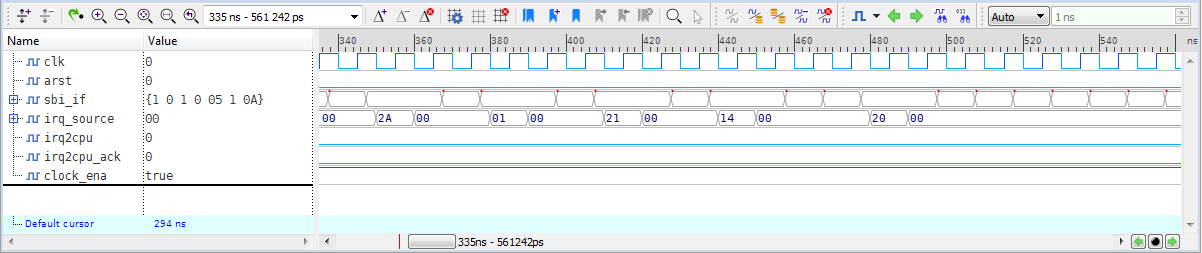

上記のすべてのステップを実行すると、以下のように結果が波形ファイルに表示される場合があります。

-

波形ファイルを保存や現在の波形設定を操作するために、Waveformメニューオプションを選択することができます。

Fig 11 - Waveformビューワ

参考文献

[1] Espen Tallaksen, “What is UVVM?”, Bitvis, Asker, Norway,2016

[2] Espen Tallaksen, “UVVM now includes OSVVM”, Bitvis , Asker, Norway,2016

-

-

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.