UVM based Verification using Riviera-PRO

Introduction to UVM

Universal Verification Methodology is a standardized methodology for verifying integrated circuit designs written in a Hardware Description Language. It consists of class libraries needed for the development of SystemVerilog based verification environment. It has set of base classes with methods as part of it. Thus, these classes makes it easier to verify the designs used in the industry.

UVM is derived from the Open Verification Methodology (OVM). UVM class libraries brings automation to the SystemVerilog language. It is completely focused upon Object Oriented Programming concepts(OOP). In this app-note we are going to discuss how to use Riviera-PRO for verification purpose using UVM (Universal Verification Methodology).

Why UVM?

UVM is a methodology based on the SystemVerilog language and is not a language on its own. It is a standardized methodology that defines several best practices in verification to enable efficiency in reusability.

Some of the benefits of using UVM are as follows:

Separating tests from testbenches – Tests in terms of stimulus/sequencers are kept separate from the actual test-bench hierarchy and hence there can be reuse of stimulus across different units or across projects.

Modularity and Reusability – The methodology is designed as modular components eg. Driver, Sequencer, Agents, env etc. which enables reusing components across unit level to multi-unit level or chip level verification as well as across projects.

Simulator Independent – The base class library and the methodology is supported by all simulators and hence there is no dependency on any specific simulator.

Sequence methodology gives good control on stimulus generation. There are several ways in which sequences can be developed which includes randomization, layered sequences, virtual sequences etc which provides a good control and rich stimulus generation capability.

Reporting mechanism – helps in debugging environment with many agents. One can filter and log messages with the help of verbosity. By changing the verbosity, printing messages can be controlled. Severity of messages are classified as fatal, error, warning, info, file name and line number where file and line are default.

Base Class Library – which provides in built methods such as compare, copy, print, reporting mechanism, macros ,etc. Extended class inherits all of above as all extended classes are derived from base class.

Configuration Class – Config class is a database where we configure all the parameters needed throughout the hierarchy using set and get. In System Verilog, we do not have such facility.

Transaction Level Modelling – In System Verilog, Mailbox is used for passing a message between components. In case of UVM, Transaction Level Modelling is used which supports multiple languages and it supports port to port connection, unlike Mailbox which has component to component connection.

Thus, there are many advantages of using UVM for verification purposes. Up next, we will see how UVM based verification takes place using Riviera-PRO.

Next, we will go through UVM’s steps of execution using Riviera-PRO.

Creating Workspace and Design

In Riviera-PRO, individual designs along with their resources can be grouped together as a workspace. The workspace allows adding and working with several designs simultaneously.

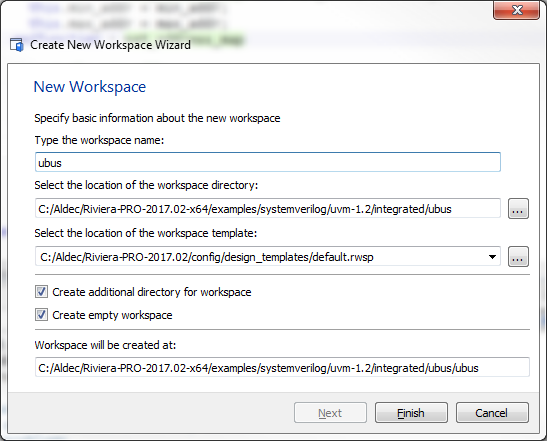

Go to File | New and click Workspace. The new Workspace wizard starts.

Type the workspace name and select the location where you want to create the project.

Click OK button when you are done.

Creating Workspace

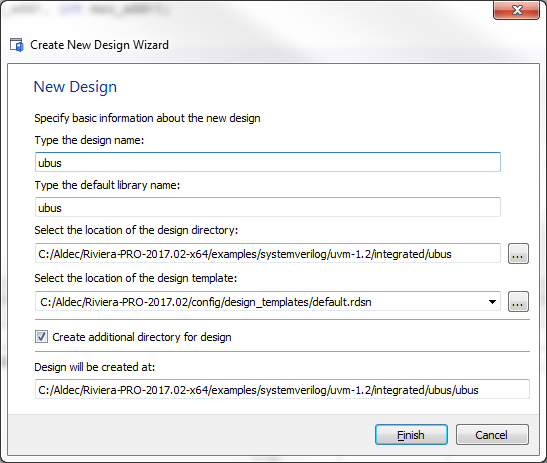

New Workspace will be created. Now right click on the workspace option and go to Add | New Design. Following window will pop up.

Creating Design

Click the first button when you are done.

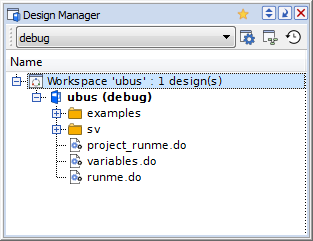

The Design Manager now shows a Workspace name and new Design attached with it.

Design Manager

Creating/Adding Files to Design

To create a new file or an existing file or to create a directory, right click anywhere into the Design Manager and click Add | New File.

You can also use File | New menu to open new files and save it to design directory.

Writing UVM

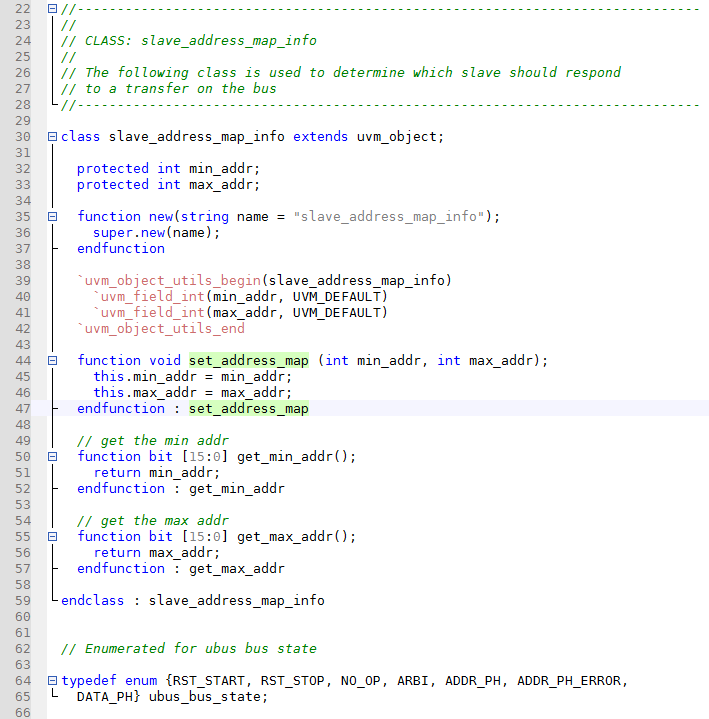

In order to create Verilog/System Verilog/System C design source files or UVM based verification testbenches, double click the Add | New File option. However, here we have provided the UVM based example implementation and we already have the file. So we have chosen Add | Existing File and attached the files that were required for implementation.

UVM Code

Compilation

Compilation is a process of analysis of a source file. Analyzed design units contained within the file are placed into the working library in a format understandable to the simulator.

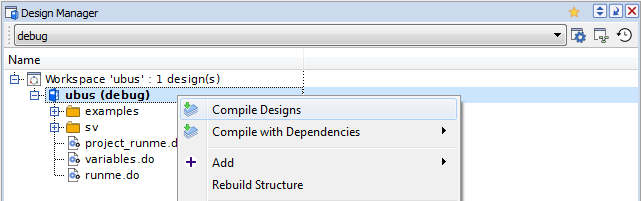

Compiling Files

If you want to compile a single file, go to the Files in the Design Manager, right click the file and choose compile from the shortcut menu.

If you choose Compile All by right clicking the Design tab for a given design, the compiler automatically reorders the source files to ensure proper sequence in which design units are compiled.

Compiling Designs

Initializing Simulation

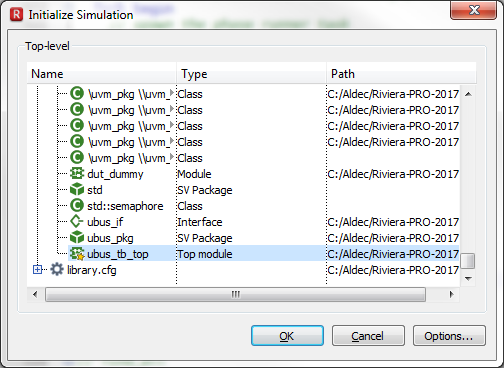

Once all needed design units have been compiled successfully, one can initialize simulation. Before initializing simulation, make sure that :

You have selected top level unit.

If you run the simulation without declaring any top-level unit, simulator will prompt you with a dialog box to select one.

To begin simulation process, choose Initialize Simulation from the Simulation window. The command launches elaboration and initialization of the simulation model. During elaboration, the simulator loads design units and builds the simulation model in the computer memory. During the initialization phase, all objects in the model acquire their initial values and all concurrent processes are executed once until their suspension.

Simulation Initialization

Selecting Testbench as Top level module

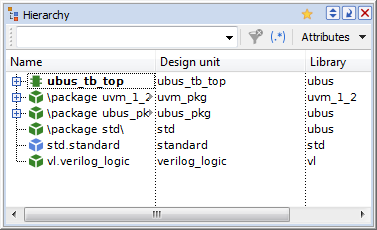

On choosing the testbench as top level instance, simulation will run and hierarchy window will appear if the simulation runs successfully.

Hierarchy Window

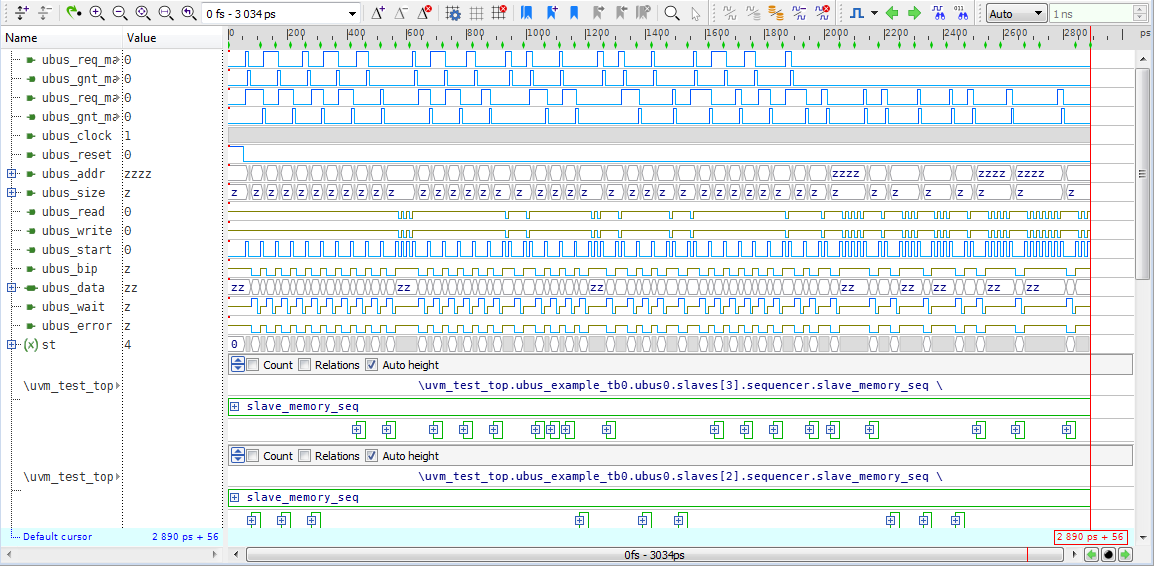

On running simulation, right click on your testbench module and choose Add to | Waveform option. Waveform Viewer will pop up.

You can run the simulation by choosing the run option available within the waveform viewer.

Waveform Viewer

On following all the steps mentioned above, you will be able to see the results into a waveform files as per below.

Waveform Viewer

To save a waveform file, to manipulate with the current waveform settings or to debug your design more thoroughly you can go and play with the Waveform debugging options.

To finish the simulation session, choose Stop Simulation from the Simulation menu.

You can always restart the simulation by selecting Restart option from the Simulation menu.

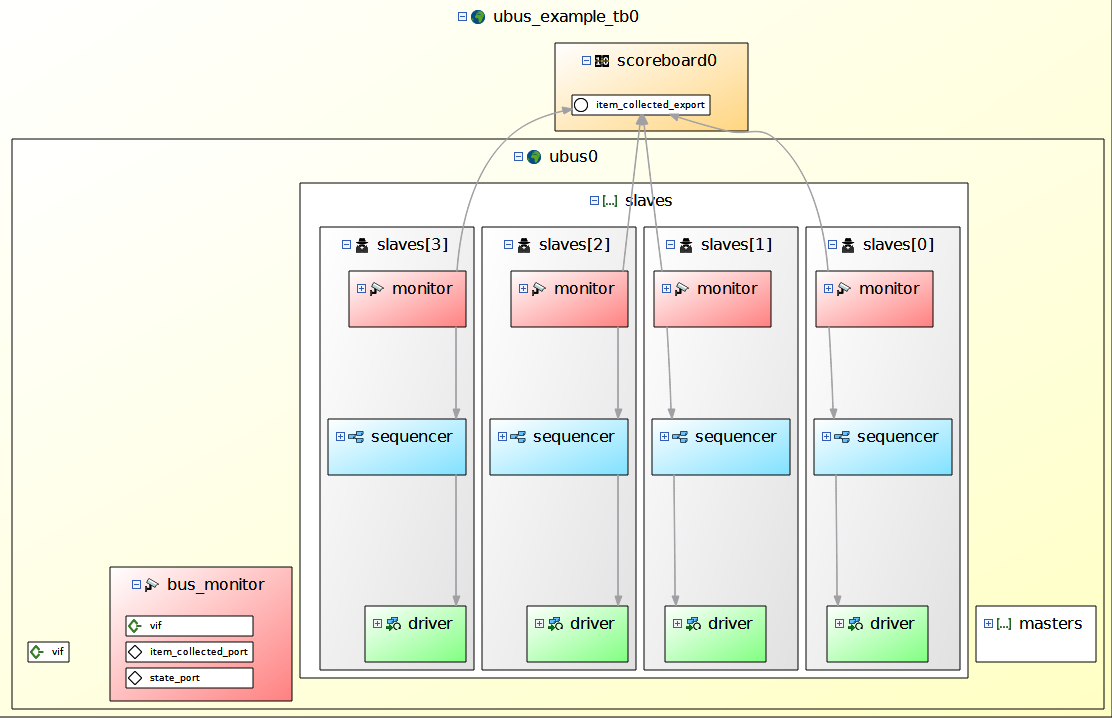

UVM Graph Window

UVM Graph is available during an active simulation session after the completion of the UVM Elaboration phase. After running the simulation, one can get access to UVM Graph Window. It enhances the ability to understand the design in an optimized way. Having a block diagram explaining the flow of execution during verification really helps debug the design well enough. To open the UVM Graph window, choose UVM Graph from the UVM Toolbar or the View | UVM menu.

UVM Graph Viewer

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.