Radiantとはじめよう

はじめに

このチュートリアルでは、RadiantでActive-HDLを使用する方法について説明します。 Active-HDLは、VHDL、Verilog、System Verilog、EDIF、およびSystemCベースのデザイン開発と検証のために設計された統合環境です。 このチュートリアルでは、Lattice Radiantが提供するVerilogデザインをサンプリングして、デザインの入力とシミュレーションを実行します。

準備

このチュートリアルを完了するには、最初にLattice Radiant Softwareと最新バージョンのActive-HDLをコンピューターにインストールする

必要があります。 無料ダウンロードはこちらから入手できます:Active-HDLおよびLattice Radiant Software。次に、Raidant Design Softwareを

実行するためのライセンスとアルデックのライセンスを要求する必要があります。

ワークスペースとデザインの作成

Lattice Radiant Design Softwareのスタートページには、さまざまなオプションがあります。 このチュートリアルでは、新しいプロジェクトを作成します。

-

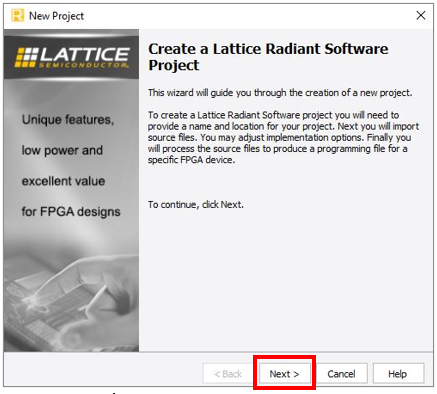

スタートページでNew Projectをクリックするか、File | New で移動しProjectをクリックします。新しいプロジェクトのウィザードが始まります。

図 1: 新しいプロジェクトの作成

-

Nextをクリック

-

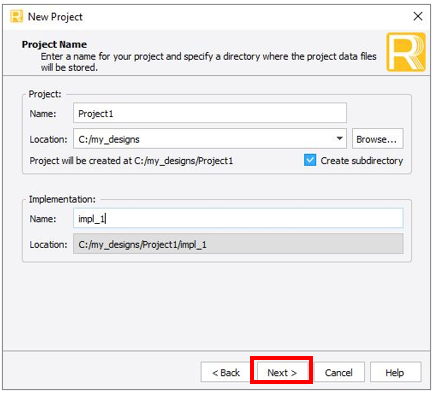

プロジェクト名を入力し、プロジェクトを保存する場所を選択します。(Browseボタンを使用して、プロジェクトディレクトリを指定できます)。サブディレクトリの作成を選択することもできます。インプリメンテーション名を入力します。

図 2: 新しいプロジェクトの作成ウィザード

-

Nextをクリック

-

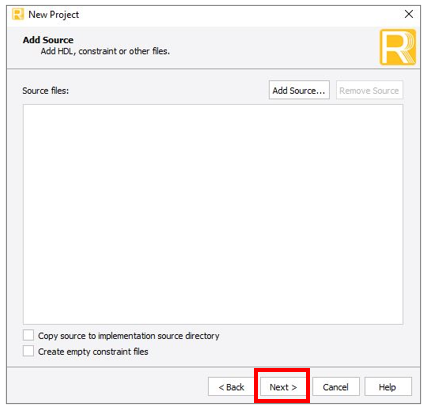

ソースファイルがある場合は、Add Sourceを選択します(Copy source to implementation source directoryおよび/またはCreate empty constraint filesを選択出来ます)。

図 3: ソースファイルの追加

-

Nextをクリック

-

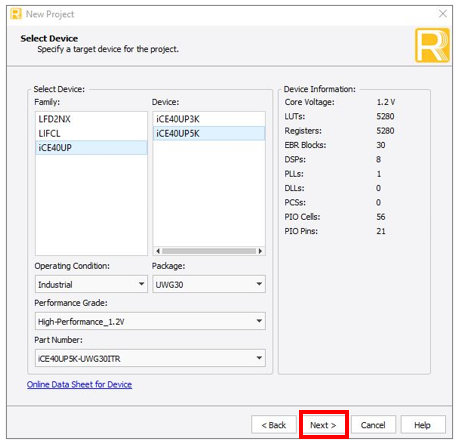

ターゲットデバイスを選択

図 4: ターゲットデバイスの指定

-

Nextをクリック

-

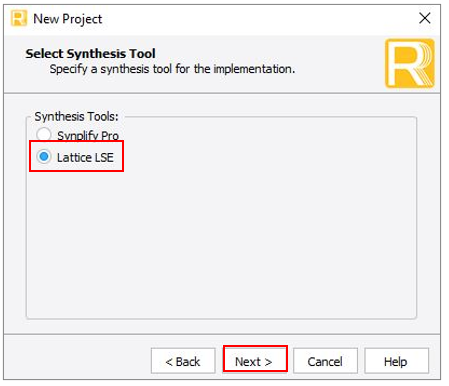

論理合成ツールを選択します。このチュートリアルではLattice LSEをクリックします。

図 5: 論理合成ツールの選択

-

Nextをクリック

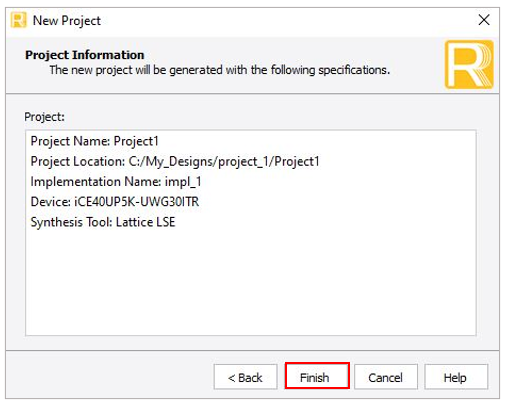

図 6: プロジェクトの情報

-

ここまで設定した内容に関するプロジェクト情報が表示されます。 すべてが正しい場合は、Finishを選択します。

デザインへのファイルの作成/追加

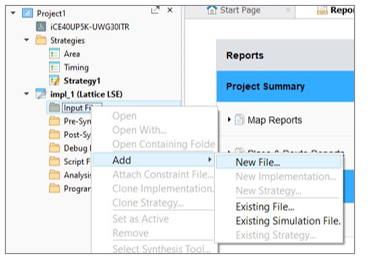

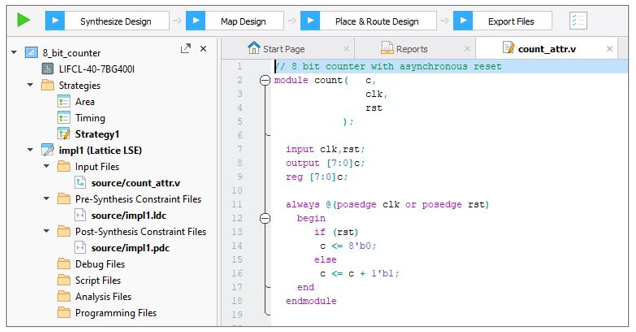

レポートとリソース使用量を含むプロジェクトの概要が表示されます。 プロジェクトの概要には、プロジェクトの階層、ソースファイル、およびコンソールを表示するペインも含まれます。

-

新しいファイルまたは既存のファイルを作成するには、Input Filesを右クリックし、Add | New Fileをクリックします。

図 7: プロジェクトにファイルを追加

注意:File | Newメニューを使用して新しいファイルの追加や、既存のファイルを開いてデザインディレクトリに保存することもできます。

HDLソースコードの作成

-

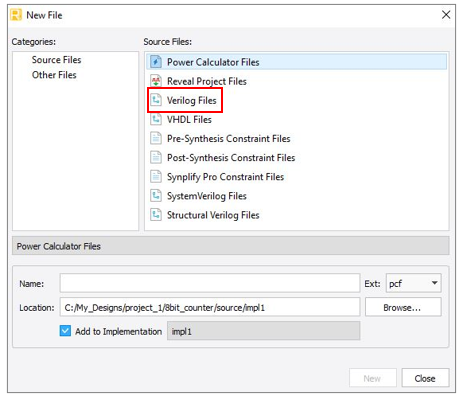

目的のソースタイプを選択し、名前を入力して、Newをクリックします。

図 8: ソースコードファイルの作成

-

エディタウィンドウが開き、デザイン入力の準備が整います。

図 9: ソースコードウィンドウ

デザインへのパスを指定

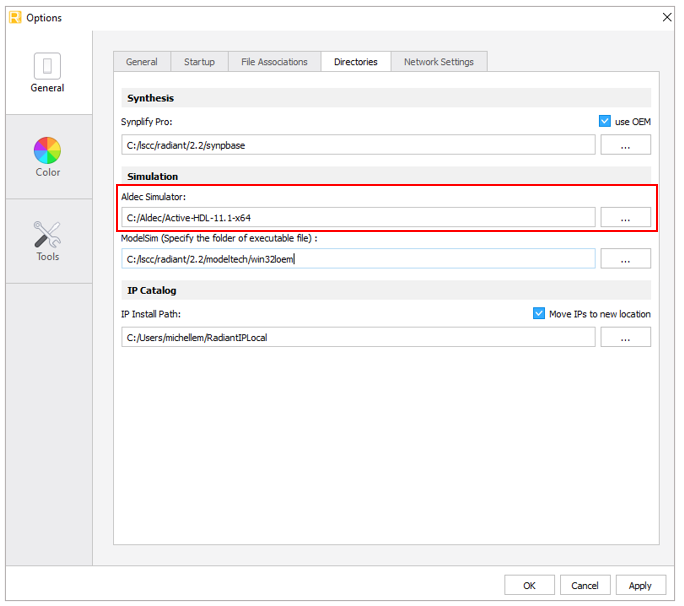

-

Tools | Options | Directories tab | SimulationでACTIVE_HDL(アルデックシミュレータ)のパスを追加します。

図 10: Active-HDLのパス

-

Applyをクリック

-

Nextをクリック

シミュレーション

-

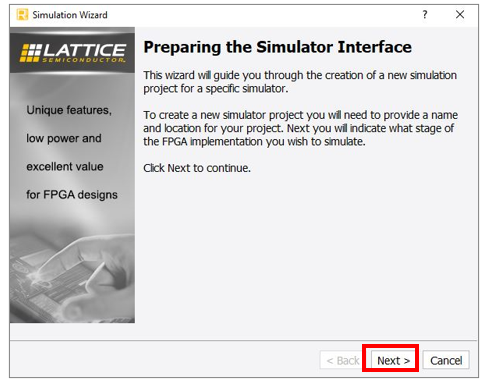

デザインをシミュレートするには、Tools | Simulation Wizardに移動します。

図 11: シミュレーションウィザード

-

CNextをクリック

-

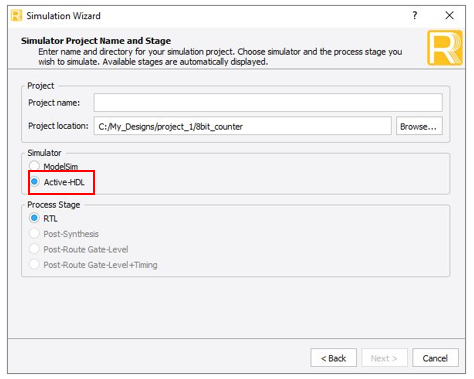

Browseを使用して、プロジェクト名とプロジェクトの場所を指定します。シミュレータとしてActive-HDLを選択し、プロセスステージを選択します。

図 12: シミュレーションプロジェクト名

-

Nextをクリック

-

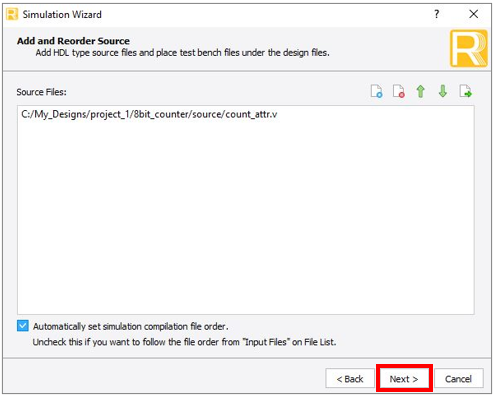

矢印を使用してファイルを整理することによりソースファイルを追加および並べ替えたり、ファイルを追加または削除したりすることもできます。

図 13: ソースファイルの追加と並べ替え

-

Nextをクリック

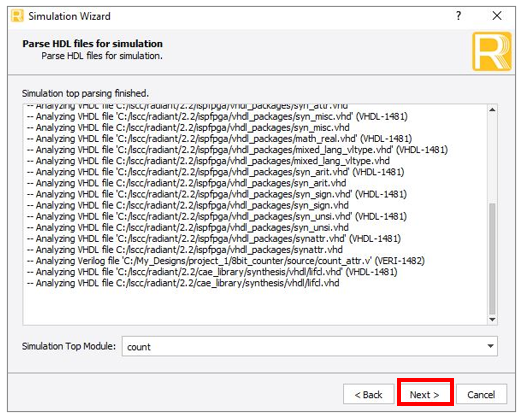

図 14: HDLファイルの解析

-

HDLファイルの解析が行われ、完了したらNextをクリック

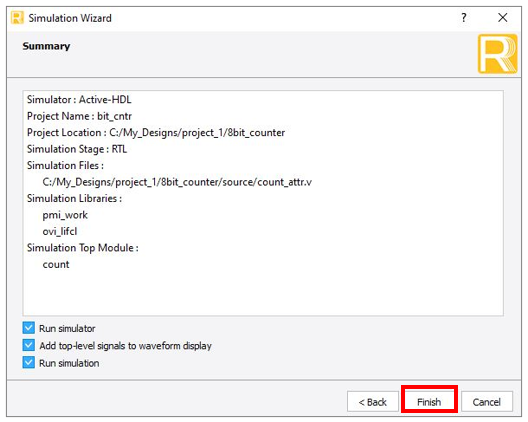

図 15: サマリ

-

サマリが提供されます。それ以外の変更が必要な場合は、back を選択し、次のオプションを確認します:

-

Run Simulatorを確認

-

Add top-level signals to waveform displayを確認

-

Run Simulationを確認

-

Finishをクリック

-

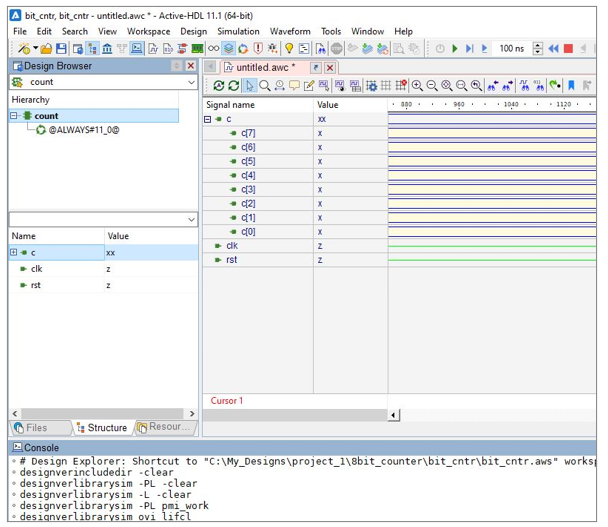

Active-HDL

-

Active-HDLが自動的に起動し、デザインブラウザ、波形ビューアおよびコンソールが表示されます。

図 16: Active-HDL

Waveformビューワ

デフォルトでは、Accelerated Waveform Viewerが有効になっており、シミュレーションの初期化時に* .asdbシミュレーションデータベースが作成されます。Accelerated Waveform Viewerは、大量のシミュレーションデータを扱うデザイナに適した選択肢です。 大規模デザインや長時間シミュレーションの実行に最適化されています。

-

Active-HDLがオープンすると、シミュレーションはすでに開始されています。 ただしSimulation メニューからRunを選択すると、不特定の時間シミュレーションを実行できます。

-

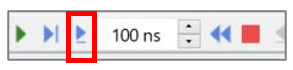

特定のタイムステップでシミュレーションを進めるには、メインツールバーにあるSimulation Step boxで目的のタイムステップを設定します。Simulation mメニューからRunを選択するか、SimulationメニューからRun Untilを選択します。シミュレーションを実行するまでの希望時間を指定してOKをクリックします。

図 17: シミュレーションの実行

シミュレーションの停止と終了

-

現在のシミュレーション時間でシミュレーションを一時停止するには、SimulationメニューからPauseオプションを選択します。

-

シミュレーションセッションを終了するには、SimulationメニューからEnd Simulationを選択します。

-

シミュレーションを再開するには、Simulation menuメニューからRestart Simulationを選択します。

オフラインで表示するために波形ファイルを保存

SimulationメニューのEnd Simulationをクリックして、保存する前にシミュレーションを停止する必要があります。

-

シミュレーションを終了するか指定された時間実行後、File | Saveメニューを使用して波形を保存できます。

ヘルプ

ツール内

Help | Product HelpメニューでActive-HDLの詳細を確認できます。

ウェブ上のヘルプ

アルデックサポートにアクセスして、Active-HDLに関するオンラインデータベースおよびその他の技術文書にアクセスしてください。

サポートアカウント

www.aldec.com/supportでAldecサポートアカウントを登録または使用して、サポートケースを開くかソフトウェアをダウンロードします。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.