Riviera-PROとQEMUを使用したZynq SoCベースシステム向けのHW/SW協調シミュレーションソリューション

ヘテロジニアスアーキテクチャの普及に伴い、HW/SW協調検証はFPGAエンジニアにとって新たな課題となっています。Xilinx Zynq FPGAデバイスは、ARMプロセッサとFPGAプログラマブルロジックで構成される、成長し続けるSoCです。ZynqなどのSoC FPGAでは、組み込みソフトウェアアプリケーションが ARMプロセッサ上で実行され、ハードウェアIPがプログラマブルロジックに実装されます。ソフトウェアとハードウェアの両方が統合され、同時に動作する新しいタイプのシステムシミュレーションが必要とされています。.

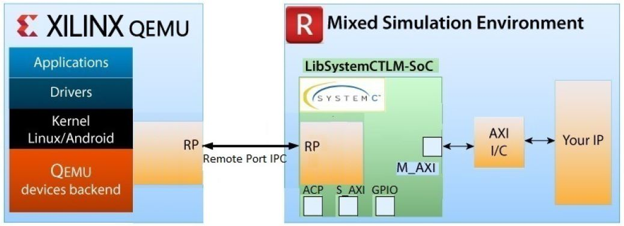

アルデックは、Riviera-PROとXilinx Quick Emulator QEMU間で、HW/SW コ・シミュレーションインターフェースを提供し、システムシミュレーションを行います。QEMUで実行されるソフトウェアアプリケーション/ドライバを使用したHDLコードのシステム統合と協調シミュレーションは、SystemCをライブラリ(LibSysytemCTLM-SoC)に完全にコンパイルすることで簡素化されました。これはRiviera-PROシミュレータで実行されます。LibSysytemCTLM-SoCは、Riviera-PROとQEMUの両方を接続するリモートポートを共有してSystemC TLMトランザクションをAXIに、またはその逆に変換して、コ・シミュレーションに高速なインタフェースを提供します。

図 1: Xilinx QEMUとRiviera-PROによるHW/SW協調シミュレーション環境

このアプリケーションノートではRiviera-PROとXilinx QEMUを使用して、Xilinx ZynqSoCベースのデザインを簡単に検証する方法を紹介します。

ソフトウェア要件:

-

Aldec Riviera-PRO 2021.10

-

Xilinx Vivado 2021.1

-

Xilinx Petalinux 2021.1

注意: PetaLinuxをインストールしていない場合、ルートユーザーでインストールしていないことを確認してください。非 root ユーザーのホームディレクトリにインストールする必要があります。

注意: Riviera-PROツールにXilinxシミュレーション・ライブラリがセットアップされていない場合、このドキュメントに従って生成してください。

制限事項:

-

Windowsには対応していません

-

対応プラットフォーム:Red Hat Enterprise Workstation/Server 7.4, 7.5, 7.6, 7.7, 7.8, 7.9, 8.1, 8.2 (64ビット版) CentOS Workstation/Server 7.4, 7.5, 7.6, 7.7, 7.8, 7.9, 8.1, 8.2 (64ビット版) Ubuntu Linux Workstation/Server 16.04.5, 16.04.6, 18.04.1, 18.04.2, 18.04.3, 18.04.4,18.04.5, 20.04, 20.04.1 (64ビット版)

-

ここでのサンプルデザインは、CentOS 7.xとUbuntu 20.04オペレーティングシステムで検証しています

プロジェクトのソースファイルの準備

コ・シミュレーションを実行するためのファイルを準備しましょう。最初のステップでは、Vivado Zynq SoCプロジェクトが必要で、これはシミュレーションモデルを生成するためにも使用されます。次にこのモデルをTLMソケットに接続し、QEMUプラットフォーム上でZynqプロセッシングシステムをエミュレートします。SW層とHW層間の通信は、リモートポートを介して行われます。コ・シミュレーションプロセスを容易にするために、アルデックはプロジェクトファイルのビルドと実行のためのスクリプトをGitHub レポジトリで提供しています。このリポジトリには、LEDを点滅させ、TySOM-1-7Z030ボードのスイッチで動作するVivadoデザインサンプルが含まれています。ユーザーは独自のデザインサンプルを使用し、GitHubフォルダで提供されているものと置き換えることもできます

ビルド済みのファイルはGitHubで公開されていますが、次章でその生成方法について説明します

Vivadoでハードウェアプロジェクトを作成

ここでは、2021.1より古いVivado バージョンにTySOMボードファイルを追加する方法についてのチュートリアルを紹介します

Vivado バージョン 2021.1 およびそれ以降の場合: 次のコマンドを実行し、システム上にダウンロードされたTySOMボードファイルのパスを追加する必要があります。

set_param board.repoPaths [

Vivadoにボードファイルを追加した後、以下の手順で操作してください:

-

Vivadoの設定をソースしVivadoを実行します

-

TySOM-1-7Z030ボードのプロジェクトを作成する

-

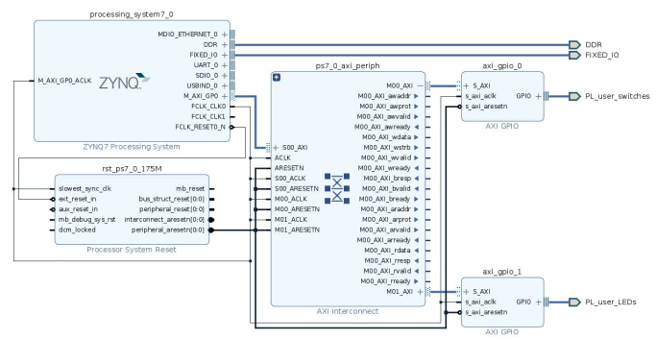

ブロックデザインを作成します

-

Zynq7 プロセッシングシステムのIPコアを追加します

-

AXI GPIO IPを2つ追加し、1つをユーザーLEDに接続し、もう1つをユーザースイッチに接続します

-

すべてに対して接続自動化を実行します

-

最終的なブロックデザインは、図2のようになります

-

axi_gpio_0(ユーザースイッチ)は0x41200000アドレスにあります。axi_gpio_1 は 0x41210000アドレスにあります。デザインを保存して検証します

-

HDLラッパを作成し、ビットストリームを生成します

-

ビットストリームを含むハードウエアをエクスポートします

-

その結果、.xsaファイルが作成され、次のステップでPetaLinuxプロジェクトを準備するために使用されます

図 2: Vivadoブロックデザイン

コ・シミュレーションのためのデザインの準備

注意: スクリプトを開始する前に、ツールへの正しいパスを設定してください。これらはconfig.shファイルに記述されています

export RIVIERA_PATH=

export PETALINUX_PATH=

export VIVADO_PATH=

ソースを生成するプロセスは、次のコマンドを実行することによって開始されます:

$ ./prepare_files.sh

注意: このステップでは、PetaLinuxプロジェクトのビルドに約30分かかる場合があります

スクリプトを実行した結果のサンプル:

PetaLinux environment set to '/edatools/Xilinx/Linux/petalinux-v2021.1' INFO: Checking free disk space INFO: Checking installed tools INFO: Checking installed development libraries INFO: Checking network and other services INFO: Create project: tysom1_petalinux INFO: New project successfully created in /home/systemc_qemu_cosim/tysom1_petalinux [INFO] Sourcing buildtools INFO: Getting hardware description... INFO: Renaming design_1_wrapper.xsa to system.xsa [INFO] Generating Kconfig for project [INFO] Silentconfig project [INFO] Extracting yocto SDK to components/yocto. This may take time! [INFO] Sourcing build environment [INFO] Generating kconfig for Rootfs [INFO] Silentconfig rootfs [INFO] Generating plnxtool conf [INFO] Adding user layers [INFO] Generating workspace directory [INFO] Sourcing buildtools [INFO] Building project [INFO] Sourcing build environment [INFO] Generating workspace directory INFO: bitbake petalinux-image-minimal [INFO] Sourcing buildtools [INFO] Building device-tree [INFO] Sourcing build environment [INFO] Generating workspace directory INFO: bitbake virtual/dtb NOTE: Started PRServer with DBfile: [INFO] Successfully built device-tree Could find Processing System in file Genenerated the following files : riviera//../src/design_1_processing_system7_0_0.vhd riviera//zynq7_compile_cosim.do riviera//all.do

コ・シミュレーションの実行

-

ソースのビルドに成功したら、最後のステップはコ・シミュレーションの処理を実行になります。これを行う最も簡単な方法は、run_example_cosim.shスクリプトを使用することです

./ run_example_cosim.sh

-

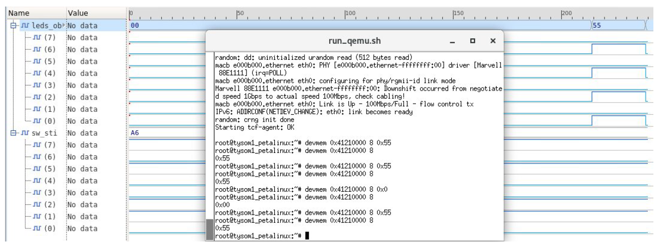

これで、QEMUのプロセスが新しいターミナルウィンドウに表示され、その間にRiviera-PROでのコ・シミュレーションが開始されます

-

Linuxシステムを起動した後、devmemコマンドを使用してLEDのテストができます:

root@tysom1_petalinux:# devmem 0x41210000 8 0x55

-

PetaLinuxウィンドウ内を変更するたびに、シミュレータを更新して新しい値を表示する必要があります。またシミュレーションを停止して再度実行することで、影響を受ける結果を確認することもできます

-

上記のコマンドを実行した後、Riviera-PROの波形ではLEDの信号が0x55の値になります

-

次のコマンドは、LEDに以前設定されていた値が読み込まれます:

root@tysom1_petalinux:# devmem 0x41210000 8

0x55

図 3: コ・シミュレーションの実行画面例

既知の問題

直面する可能性のある既知の問題がいくつかあります

-

Linuxシステムは、下記記述でがかなり長い時間ハングする可能性があります:

random: crng init done

Starting tcf-agent: OK

-

コ・シミュレーションが終了したら、最初にRiviera-PROをオフにしてkら、QEMUをオフにすることをお勧めします。コンソールでのクラッシュは逆の順番で表示されることがあります

-

"fs.inotify.max_user_watches" が不足している可能性があり、下記のエラーが発生します:

ERROR: No space left on device or exceeds fs.inotify.max_user_watches? ERROR: To check max_user_watches: sysctl -n fs.inotify.max_user_watches. ERROR: To modify max_user_watches: sysctl -n -w fs.inotify.max_user_watches=

. ERROR: Root privilege is required to modify max_user_watches. 次のコマンドを使用して、この値を増やすことができます:

sysctl -n -w fs.inotify.max_user_watches=

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.