Active-HDLでPlatform Designerで作成したシステムの機能シミュレーションを実行

はじめに

このドキュメントでは、Active-HDLでIntel Platform Designerプロジェクト(旧Qsys)の機能シミュレーションを実行するために必要な手順について説明します。フローを説明するために、Platform Designerのシステムデザインチュートリアルを使用します。

必要条件と制限

このアプリケーションノートでは、以下を前提としています:

-

以下のソフトウェアがインストールされ、ライセンスが付与されていること:

-

Intel Quartus® Prime Pro 23 以降と、必要なすべてのデバイスがインストールされていること。

Active-HDL 15以降

-

-

このアプリケーションノートで使用するPlatform Designerのシステムデザインチュートリアルのサンプル(qsys_pro_tutorial_design_arria_10_17p0.zip)をダウンロードしました。Platform Designer Tutorial Design Exampleの Web ページからダウンロードできます。

Platform Designer でデザインを生成する

-

qsys_pro_tutorial_design_arria_10_17p0.zipアーカイブを解凍します。このドキュメントはC:\ rootフォルダを使用します。

-

Quartus Prime Proの環境を開きます。

-

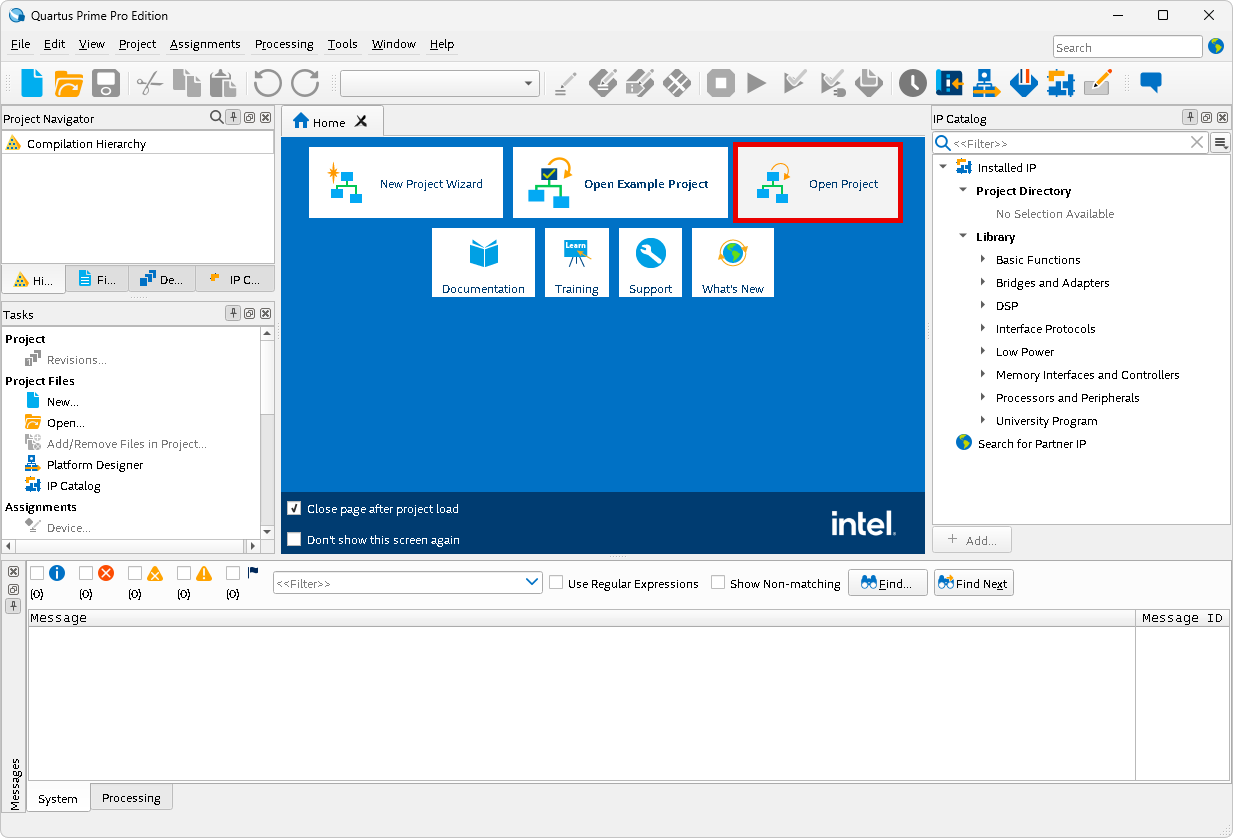

HomeページにあるOpen Projectボタンをクリックし、解凍したアーカイブのメインフォルダからA10.qpfファイルを選択します。

Figure 1. Quartus Prime Proの環境

-

左側のTasksペインまたはToolsメニューからPlatform Designerを選択し、Platform Designerを開きます。

-

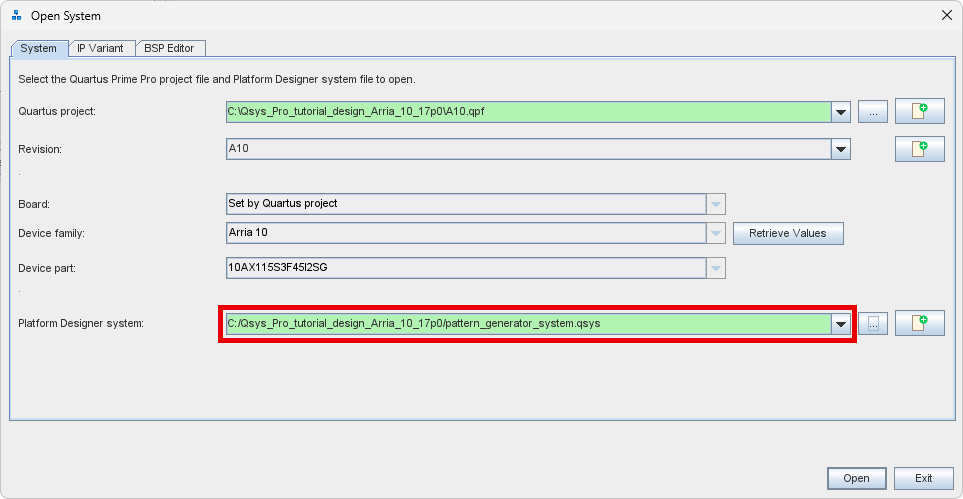

Platform Designer の起動時に表示されるOpen Systemウィンドウで、SystemタブのPlatform Designer systemフィールドに pattern_generator_system.qsys ファイルを指定します。次に、Openボタンでデザインを開きます。

Figure 2. Platform DesignerのOpen Systemウィンドウ

NOTE: オープン時、デザインで使用されているすべての IP コアを最新バージョンにアップグレードするよう求められます。プロンプトが表示されたらこの操作を確認し、完了後にデザインを保存します。

-

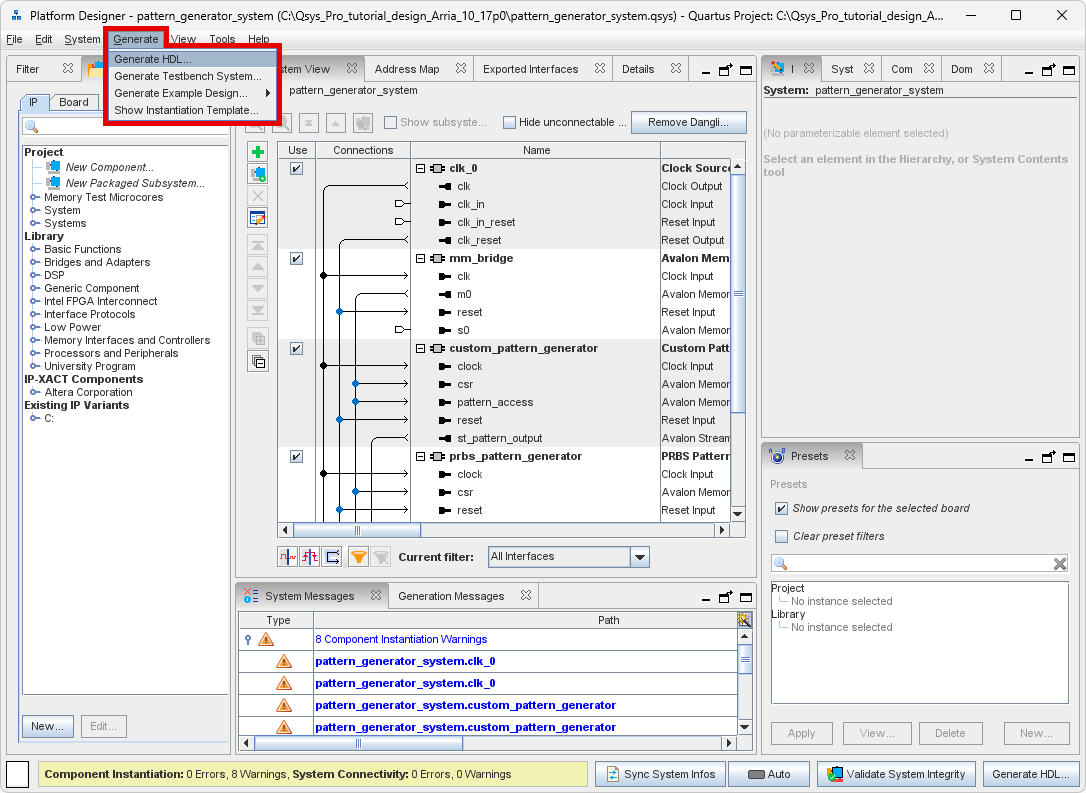

MainメニューのGenerateメニューから、Generate HDLオプションを選びます。Generationウィンドウが開きます。

Figure 3. Platform Designerの環境

-

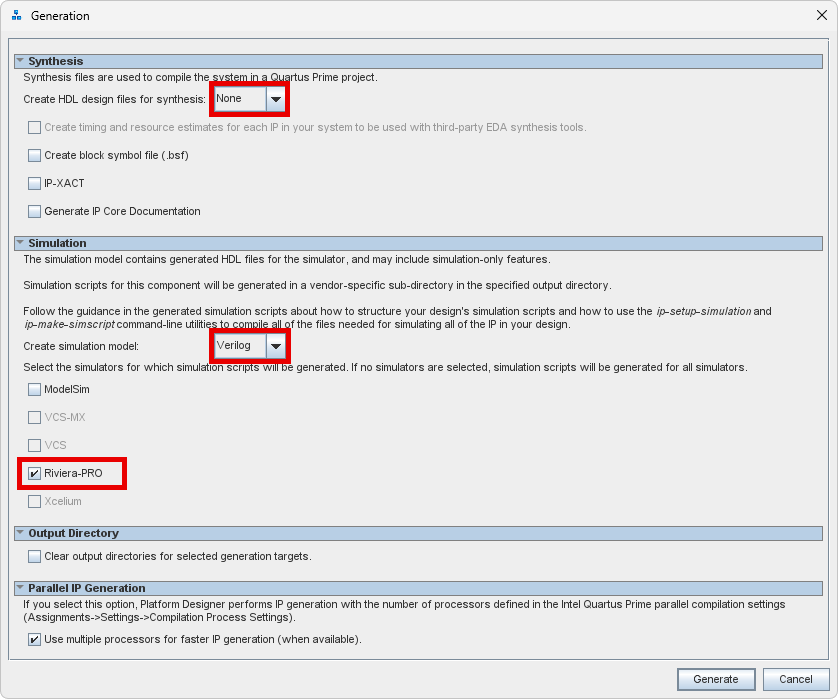

GenerationウィンドウのSynthesisカテゴリーで、Create HDL design files for synthesisリストのNoneを選択し、すべてのチェックボックスをオフにします。

-

Simulation カテゴリーで、Create simulation modelリストからVerilogを選び、Riviera-PROチェックボックスが選択されていることを確認します。

Figure 4. Platform DesignerのGeneration ウィンドウ

-

Generate ボタンをクリックして生成プロセスを開始します。

-

Platform Designerでシミュレーション・モデルを生成すると、rivierapro_setup.tclスクリプトがQsys_Pro_tutorial_design_Arria_10_17p0\pattern_generator_system\sim\aldecフォルダに生成されます。

Platform Designerデザインのシミュレーション実行

-

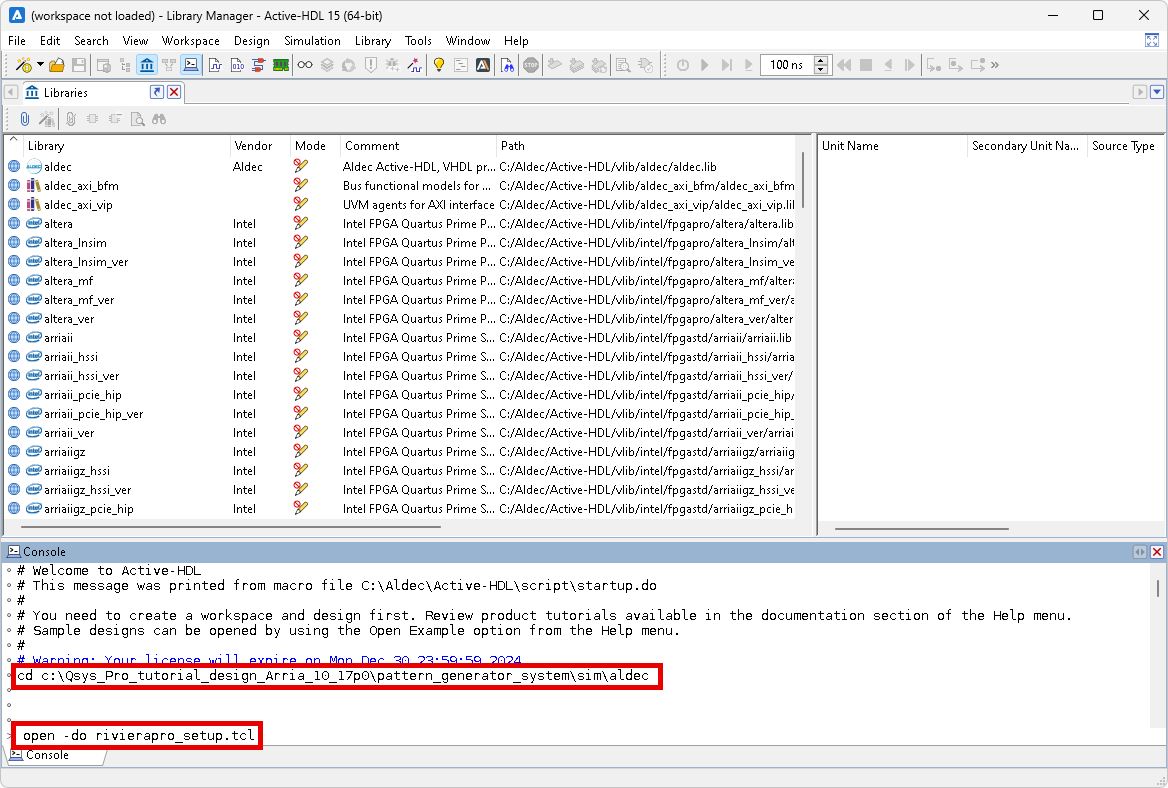

Active-HDL.を開きます。rivierapro_setup.tclスクリプトを指すように場所を変更します。コンソールから次のコマンドを実行します:

cd C:\Qsys_Pro_tutorial_design_Arria_10_17p0\pattern_generator_system\sim\aldec

Figure 5. Active-HDL.のPlatform Designerスクリプトにアクセス

-

rivierapro_setup.tclスクリプトを開きます。コンソールから次のコマンドを実行します:

open -do rivierapro_setup.tclこのスクリプトは必要な環境変数を設定し、必要なライブラリのコンパイル、デザインファイルのコンパイル、シミュレーションの初期化を行うエイリアスを宣言します。スクリプトはそのまま実行できますが、必要に応じてエイリアスを変更することもできます。下の表はエイリアスコマンドの説明です:

エイリアス

内容

dev_com

デバイスライブラリファイルのコンパイル

com

デザインファイルのコンパイル

elab

トップレベルデザインを作成し、シミュレーションを初期化します。トップレベルデザインはスクリプトのTOP_LEVEL_NAME変数で定義

elab_debug

最適化を無効にして(-dbgと-o2がasimに渡される)トップレベルデザインをエラボレートし、シミュレーションを初期化

ld

すべてのライブラリとデザインファイルをコンパイルし、トップレベルデザインをエラボレートし、シミュレーションを初期化

ld_debug

すべてのライブラリとデザインファイルをコンパイルし、トップレベルデザインをエラボレートし、最適化を無効にしてシミュレーションを初期化(-dbgと-o2が渡されます) Table 1. rivierapro_setup.tclスクリプトで定義されたエイリアス

-

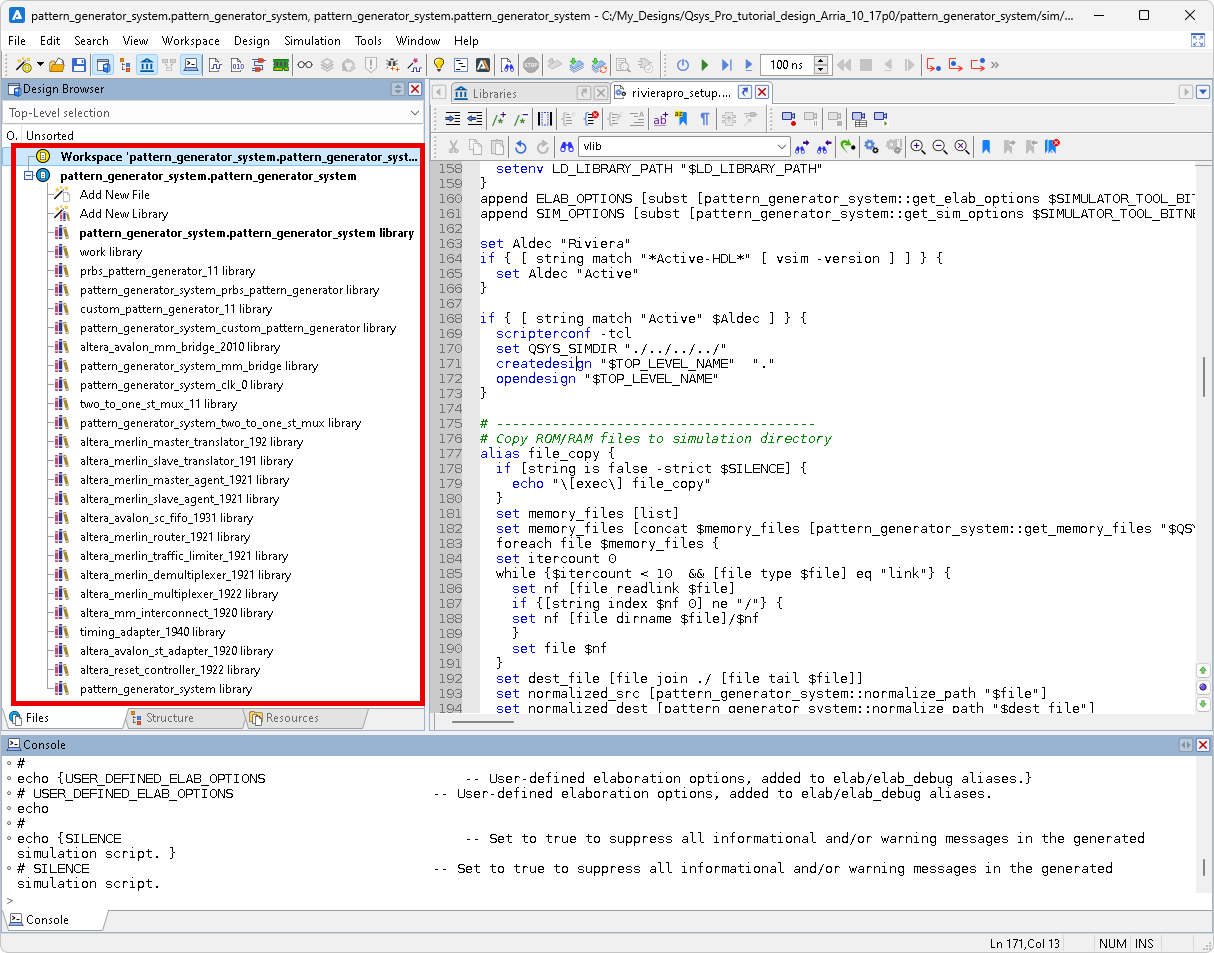

次の式がif文の条件でチェックされるコード行に移動します:

[ string match "Active" $Aldec ]

Active-HDL でデザインをロードした後、正しい場所を指すようにステートメント本体で QSYS_SIMDIR 変数を更新する必要があります。この変更を適用すると、ステートメントは次のようになります:

if { [ string match "Active" $Aldec ] } { scripterconf -tcl set QSYS_SIMDIR "./../../../" createdesign "$TOP_LEVEL_NAME" "." opendesign "$TOP_LEVEL_NAME" }

-

スクリプトを実行します。コンソールから以下のコマンドを実行します:

do rivierapro_setup.tcl

スクリプトが実行されると、新しいデザインが作成され有効になります。

Figure 6. Platform Designerで作成したシステムをActive-HDLでロード

-

コンソールからdev_comコマンドを実行します。

NOTE: Intelライブラリがすでにインストールされている場合は、この手順を省略できます。

これにより、以下のライブラリーがコンパイルされます:

-

altera, altera_ver

-

altera_lnsim, altera_lnsim_ver

-

altera_mf, altera_mf_ver

-

lpm, lpm_ver

-

sgate, sgate_ver

-

twentynm, twentynm_ver

-

twentynm_hip, twentynm_hip_ver

-

twentynm_hssi, twentynm_hssi_ver

-

-

コンソールからcomコマンドを実行します。デザインソースファイルがコンパイルされます。

-

コンソールからelabコマンドを実行します。シミュレーションが初期化されます。

-

コンソールからrun 40usコマンドを実行してシミュレーションを実行します。

まとめ

Intel Platform Designer プロジェクトはActive-HDLで正常にシミュレーションできます。Intel Platform Designerでのシステム作成の詳細については、次のリンクを参照してください:

https://www.intel.com/content/www/us/en/docs/programmable/683364/18-1/creating-a-system-with.html

Active-HDLでPlatform Designerプロジェクトのシミュレーションがうまくいかない場合は、カスタマーポータルからアルデックサポートに連絡してください。

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.