Active-HDLとSimulink®のインターフェース

概要

近年、プログラマブル・ロジック・デバイスは、特にデジタル通信、ネットワーキング、ビデオ、およびイメージング等の高性能デジタル信号処理(DSP)システムを実装するのに重要なキーコンポーネントとなっています。しかし、C言語またはアセンブリ言語でのプログラミングに精通しているDSP設計者は、多くの場合VHDLまたはVerilogなどのハードウェア記述言語(HDL)を使用するデジタル設計には慣れていません。VHDLには、多くの抽象度の高いシミュレーションのための言語構造を提供しますが、その合成サブセットはシステム設計にとっては制限が厳しすぎます。MathWorks社のMATLAB®/Simulink®シミュレーション環境は、広くアルゴリズム開発と検証に使用できるDSPシステムのための強力な高レベルの数学的モデリング環境を提供しています。

Active-HDLはMATLAB®およびSimulink®シミュレーション環境へのインターフェースを提供することで、ハードウェア記述言語を使用て記述されたビヘイビア・モデルと数式を使用して記述された機能ブロックとの協調シミュレーションを可能にします。Active-HDLインストレーションプログラムと共に提供されるインタフェースでは、Simulinkで実行される検証プロセスの中でブラックボックスとして使用されるモジュールまたはエンティティを選択することができます。それはVHDLおよびVerilogデザインの両方を使用することができ、mlab_cosim.dllライブラリ($ALDEC\Simulink)を通してMATLAB環境とインターフェースを行います。Simulinkのインターフェースは次のようなメリットをユーザーに提供します:

-

DSPシステムにおけるHDLシミュレーションと高レベルの数学的モデリング環境との間のギャップを埋める直感的なインターフェイス

-

Simulink環境とActive-HDL波形ウィンドウの両方でシミュレーション結果を表示

-

Acive-HDLとSimulink間での自動的な値の変換

-

Xilinx System Generatorを統合し、テスト対象のユニットを刺激するために使用される複雑な数式を使用した高度なテストベンチ

トップレベル・インターフェースからINOUTポート宣言を削除

Simulink®はブロック上にある双方向(INOUT)ポートの概念をサポートしていません。そのような理由により、もしトップレベルのコンポーネントのインターフェース(VHDLまたはVerilogのどちらか)に入出力ポートが含まれている場合、協調シミュレーションのプロセスを続行する前に単一方向のポートに変換する必要があります。以下のVHDLコード例はこれを行う方法について示しています。

変更前:

entity FPC is port ( VCO: in BIT; RF: in BIT; RESET: in BIT; PLL_LOCK: out BIT; DOWN: inout BIT; UP: inout BIT ); end FPC; architecture FPCPLL of FPC is signal S1,R2,Rs : BIT; signal NAND1, NAND6, NAND7, Q1, QB2: BIT; begin NAND1 <= not(VCO and DOWN); NAND6 <= not(RF and UP); NAND7 <= '0' when RESET = '1' else not(NAND1 and Q1 and QB2 and NAND6); DOWN <= not(NAND1 and Q1 and NAND7); UP <= not (NAND6 and QB2 and NAND7); ... end architecture;

変更後:

entity FPC is port ( VCO: in BIT; RF: in BIT; RESET: in BIT; PLL_LOCK: out BIT; DOWN: out BIT; UP: out BIT ); end FPC; architecture FPCPLL of FPC is signal S1,R2,Rs,s_up,s_down : BIT; signal NAND1, NAND6, NAND7, Q1, QB2: BIT; begin NAND1 <= not(VCO and s_down); NAND6 <= not(RF and s_up); NAND7 <= '0' when RESET = '1' else not(NAND1 and Q1 and QB2 and NAND6); s_down <= not(NAND1 and Q1 and NAND7); s_up <= not (NAND6 and QB2 and NAND7); DOWN <= s_down; UP <= s_up; ... end architecture;

インターフェースの仕様

Active-HDLは以下のMathWorksシミュレーションツールとのインターフェースを提供します:

-

MATLAB

-

Simulink

インターフェースがサポートする機能:

-

出力のデータタイプ: Boolean, Unsigned, Signed (2's comp)

-

ビット数: 1~52の間の整数値

-

小数点: 0 ~ 51

-

量子化: 切り捨て, 丸め

-

オーバーフロー: 飽和, 不飽和, エラー

Simulinkインターフェースのセットアップ

最初にMATLABでインターフェイスのセットアップを実行するには、以下の設定手順に従って実行してください:

-

MATLABを起動します。

-

MATLABウィンドウで現在のフォルダを$aldec\simulinkディレクトリに変更します。

-

MATLABコマンドウィンドウでsetupコマンドを入力し、Enterキーを押します。MATLABにインストールされた以前のバージョンのActive-HDLブロックセットを誤って削除しないために、警告のダイアログボックスが表示されます。継続するには、Yesをクリックします。次のメッセージがコマンドウィンドウに表示されます:

Welcome to Active-HDL Blockset Setup.

Removing previous version of Active-HDL Blockset from path:

c:\Aldec\Active-HDL\Simulink

Installing Active-HDL Blockset...

Adding Active-HDL Blockset path:

C:\Aldec\Active-HDL\Simulink

Active-HDL Blockset has been installed successfully.

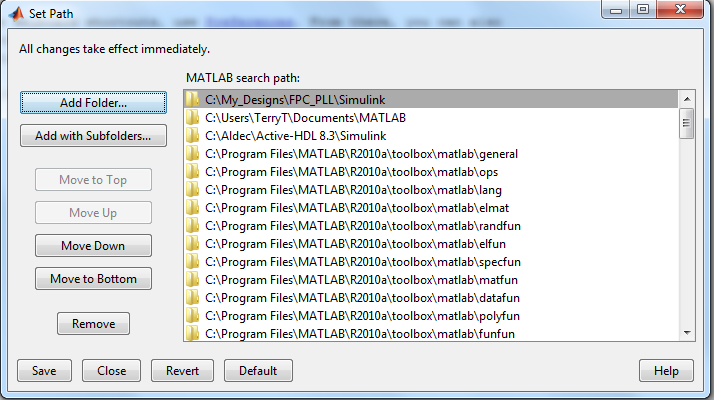

- メニューからパスの設定をクリック

このウィンドウで協調シミュレーションに必要なファイルの一部が含まれている<Active-HDL Installation>\Simulinkフォルダに検索パスを設定する必要があります。保存オプションを選択し、閉じるボタンを押してパスの設定ウィンドウを閉じます。

Active-HDLで協調シミュレーションを行うための準備

MATLABのSimulink環境で協調シミュレーションプロセスを開始するには、初めにHDLモデルの最上位レベルのエンティティまたはモジュールに対するSimulink記述ファイル(.m)を生成する必要があります。Active-HDLは自動的にこれらを行うことができます。Active-HDLで次の手順を実行します:

-

ワークスペースを開き、協調シミュレーションするHDLユニットが含むデザインをアクティブに設定します。

-

Simulinkで協調シミュレートするモデル(以下の例ではfpc.vhd)のHDLファイルをコンパイルします。

-

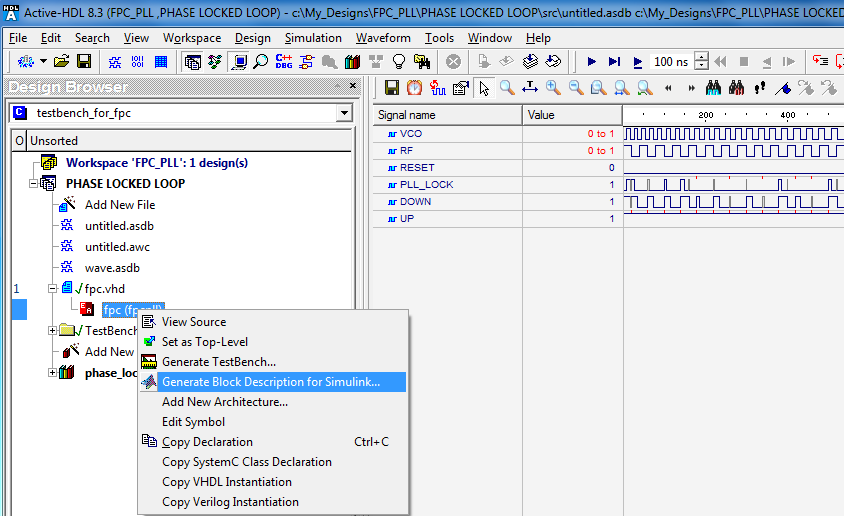

SimulinkでHDLブラックボックスとして使用されるトップレベルのデザインユニットのソースファイル(例えばfpc.vhd)を展開します。ユニット(例えばFPC(fpcpl))を右クリックし、ポップアップメニューから、 Generate Block Description for Simulink を選択します。

設計ライブラリが空の場合、このオプションは使用できません。

-

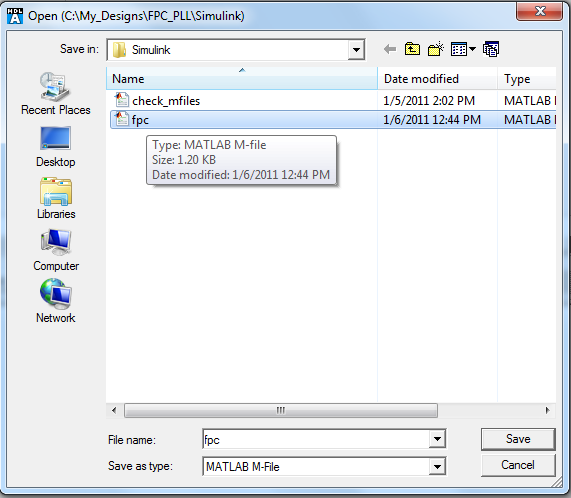

保存をクリックしてMATLAB Mファイルを生成します。

コンソールに次のメッセージが表示されます:

simulinkgenmod -f -o "C:\My_Designs\FPC_PLL\Simulink\fpc.m" fpc fpcpll

# Generating block description file: 'C:\My_Designs\FPC_PLL\Simulink\fpc.m'...

# Generation of block description file for "fpc (fpcpll)" completed successfully.

注意: Simulinkのダイアグラム上で複数のHDエンティティをシミュレートする場合は、各ブロックの記述を生成する必要があります(各エンティティ/アーキテクチャ・ペアごとに.m ファイルを作成)。Simulinkとの協調シミュレーションを行う際に、MATLAB Simulinkでシミュレートする全てのHDLコンポーネントの出力ディレクトリが同じパスになっていることを確認ください。

-

Active-HDLを終了します。

Simulinkで協調シミュレーションを実行

-

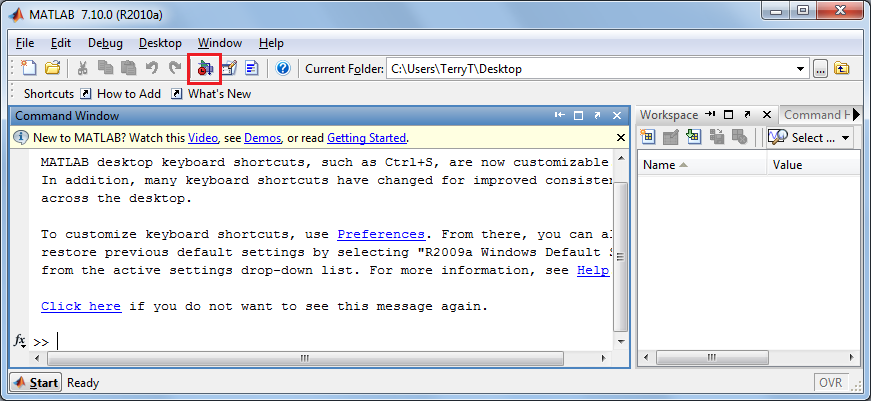

MATLABのメインウィンドウで、Active-HDLで.mファイルを生成した場所を現在のフォルダに設定します。この例ではC:\My_Designs\FPC_PLL\ Simulinkになります。

-

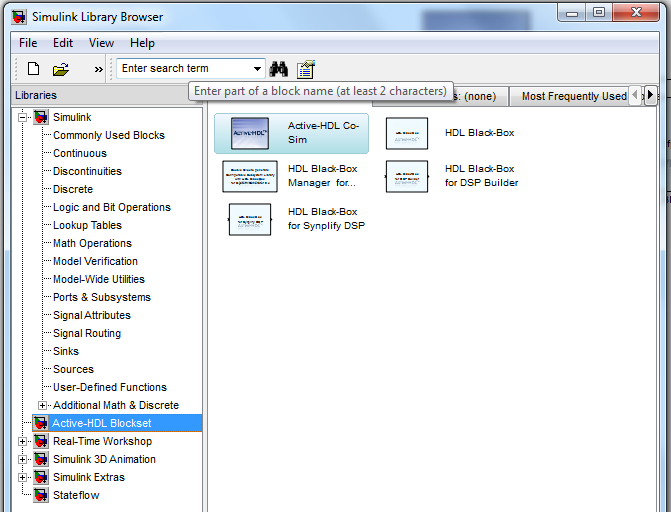

MATLABのメインツールバーからSimulinkアイコンをクリックし、Simulinkライブラリブラウザーのウィンドウを開きます。Simulinkライブラリブラウザーのウィンドウの左ペインで、Active-HDL Blocksetライブラリが表示されます。

Simulinkライブラリブラウザーウィンドウに表示される全てのブロックは、Simulinkモデルウィンドウに追加することができます。 Simulinkモデルの作成についての詳細は、Simulinkのオンラインマニュアルを参照してください。

-

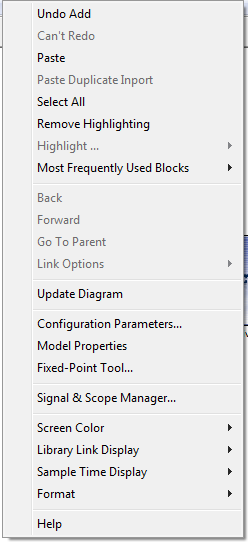

新しいSimulinkモデルを作成し、モデルのプロパティ画面を表示するため空きスペースを右クリックします。

-

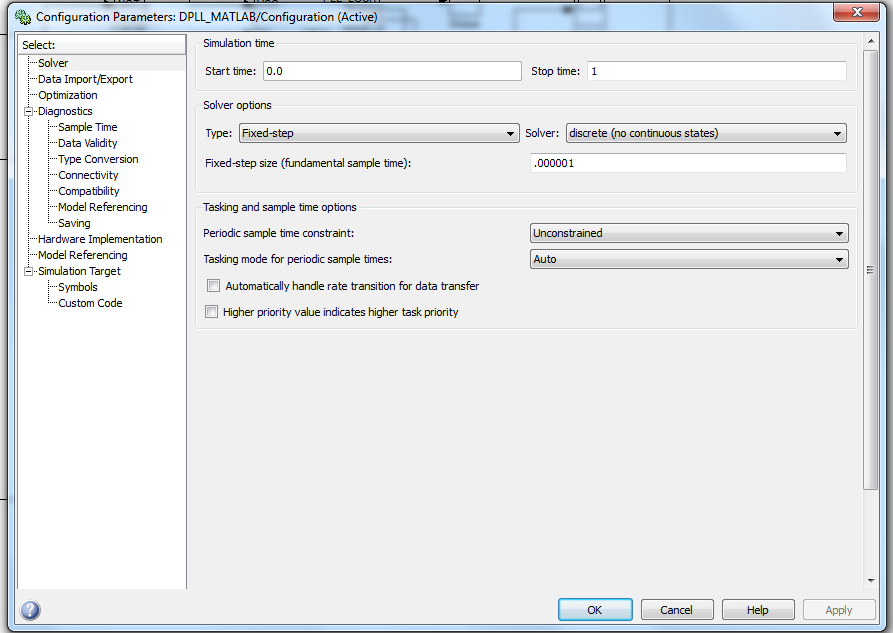

モデルコンフィギュレーションパラメータを選択し、マウスをクリックします。以下の画面が表示されます。

-

ソルバーを"discrete (no continuous states)"に、タイプを"固定ステップ"に設定。希望するサンプル時間を固定ステップに設定します(1usはシミュレーション時間で毎秒1,000,000のサンプルを意味する、すなわち1秒のシミュレーションで100万のサンプルとなる)。周期的なサンプル時間の制約を"制約無し"に、周期的なサンプル時間のタスクモードを"自動"に設定します。

-

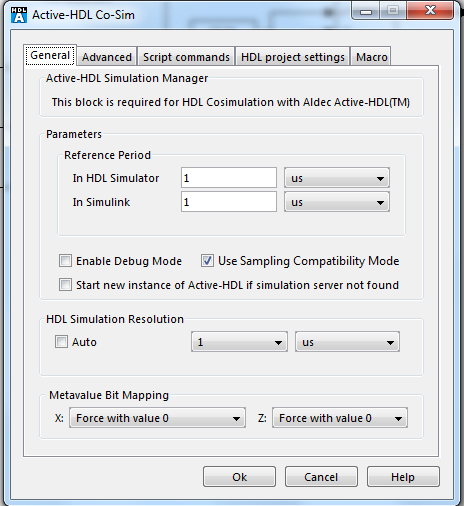

SimulinkモデルへActive-HDL Co-Simブロックを追加し、ダブルクリックしてブロックを開いて参照してください。

-

HDL SimulatorとSimulinkのReference Periodを所望の周期に設定します。上記では1usが選択されています。Use Sampling Compatibility Modeがチェックされていること、他は選択されていないことを確認します。HDL Simulation ResolutionがReference Periodと一致するように設定します。そうでないとタイムスキューが発生します。他はデフォルトから変更せずOKをクリックします。

-

デザインの協調シミュレーションを実行する前に、HDL Black-BoxとActive-HDL Co-Simブロックの両方で追加のパラメータを指定する必要があります。

-

最後にAHDLとSimulinkを協調シミュレーションするため、各エンティティのBlack Boxを追加します。

以下のようにBlack BoxのSimulinkブロックを追加します。

-

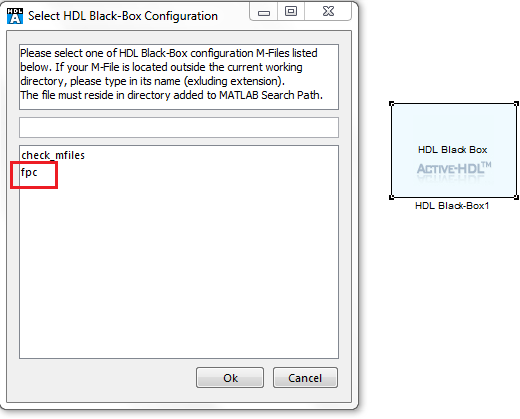

適切な"entity.m"ファイルを(この例ではFPC)を選択し、OKをクリックします。ブラックボックスは、ブロックの中央にエンティティ名が表示されモデルが追加されます。

-

ボックスをダブル・クリックしパラメータを変更できますが、特にデフォルトの設定を変更する必要はありません。

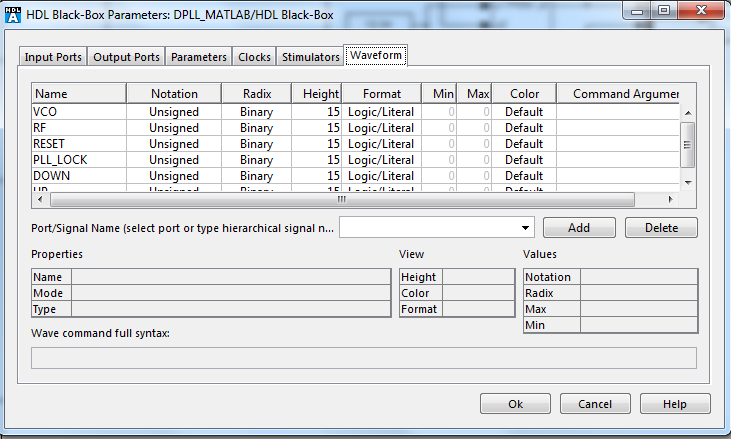

波形をActive-HDLで表示する場合はWaveformタブを選択し、以下に示すように所望の信号を選択してADDボタンをクリックします。

-

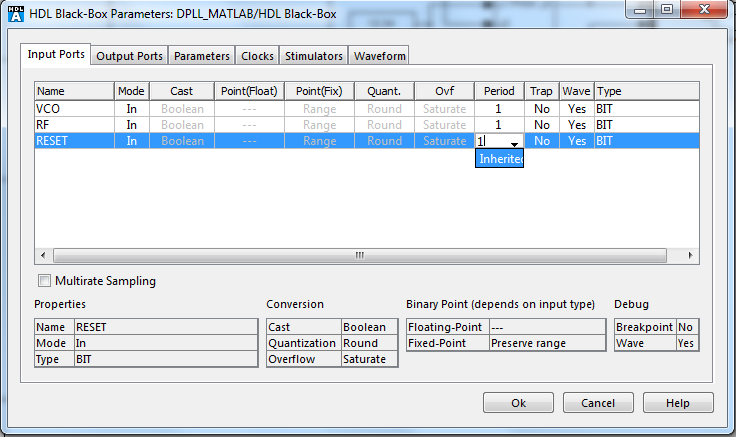

以下のように、InputおよびOutputのPeriodを"1"に設定することが重要です。

Input Portsタブを選択し、各信号のPeriodを"Inherited"から"1"に変更することを確認します。

-

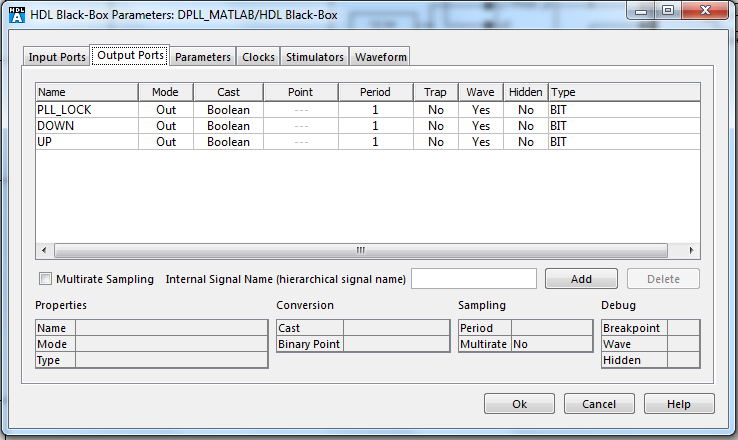

以下のようにOutput Portsタブを選択し、各信号のPeriodを"Inherited"から"1"に変更することを確認します。

OKをクリックしてダイアログボックスを閉じます。

-

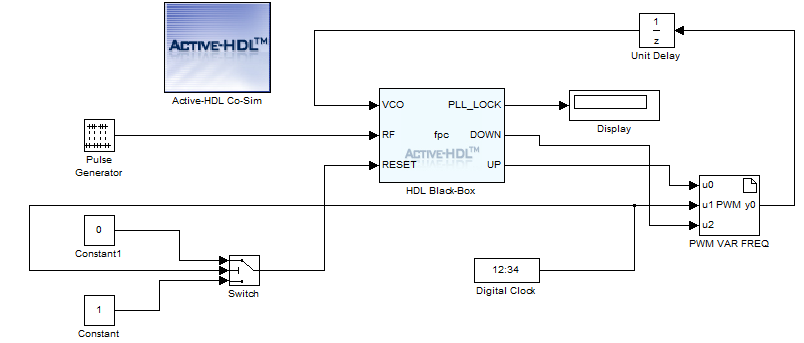

Black Boxの周囲にテストベンチを構築して、協調シミュレーションのためのMATLA/Simulinkモデルを完成させます。

注意: MATLAB Simulinkモデル内のHDL Black Boxに接続されたすべてのS-Functionブロックを再構築することが重要です。これは協調シミュレーションのプロセス中にAHDLの異常やタイムスキューを発生させます。

-

次のステップは、完了時にMATLAB/Simulinkモデルを保存し、AHDLがロードされていないことを確認します。注意:SimulinkのUnit Delayブロックが上記のようにS-functionの出力とHDL Black-Boxの入力の間での適切な協調シミュレーションのために必要となります。

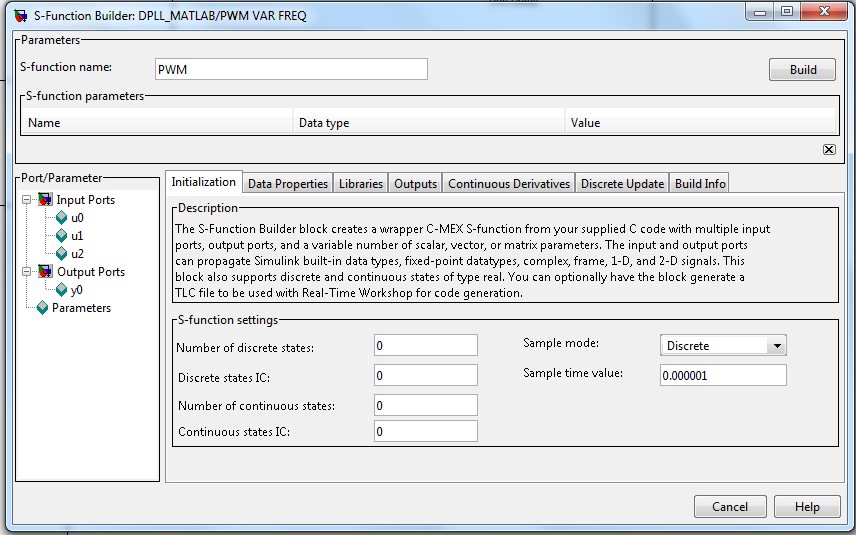

S-functionが使用される場合、以下のようにタイミングはモデルのコンフィギュレーションに一致するよう設定する必要があります(サンプル・モードは"Discrete"で、サンプル時間の値はモデルのサンプル時間に設定する)。

-

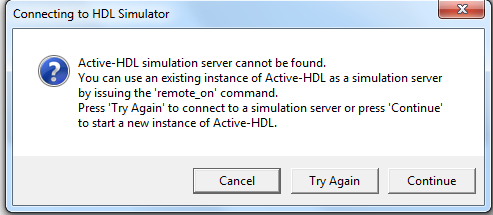

MATLAB/Simulinkのシミュレーションを実行すると以下のダイアログが出力され、"続行"ボタンをクリックするとAHDLが自動的に起動します。AHDLのクライアントとの接続行われ、シミュレーションが完了するまで実行されます。

-

新しいシミュレーションのたびにAHDLを再起動する必要はありません。MATLAB/Simulinkモデルで必要な変更を行い、必要に応じてモデルを保存し、MATLAB/Simulinkのシミュレーションを再実行することができます。

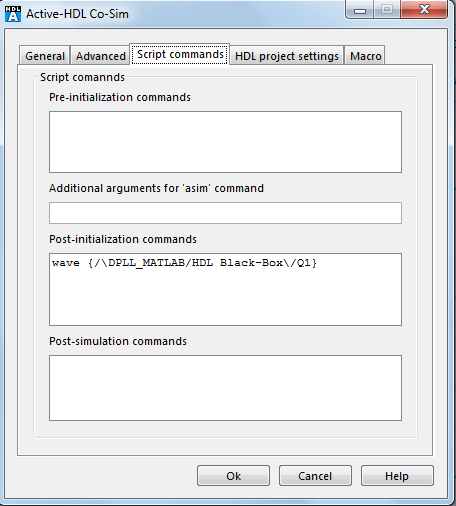

Simulinkからポートに無い信号をActive-HDL波形ビューアに追加する

HDL Black Boxの波形がActive-HDLで必要な場合は(Black BoxのOutputまたはInputとして存在しない場合)Active-HDL Co-Simブロックを開き、Script commandsタブを選択して、所望の信号をwaveコマンドと中括弧"{}"で入力します。

このwaveコマンドのパラメータは、シミュレーションの初期化の後にActive-HDLでのコマンドコンソールに信号名をドラッグすることで容易に得ることが可能です。表示された適切なパスをActive-HDL Co-SimブロックのPost-initialization commandsのスクリプトコマンドにコピー&ペーストします。

# Simulation has been initialized

# Selected Top-Level: dpll_matlab (cosimulation)

# /\DPLL_MATLAB/HDL Black-Box\/Q1 --console output from dragging waveform to command console window

# wave {/\DPLL_MATLAB/HDL Black-Box\/Q1} --add wave command and surround in braces

# 1 signal(s) traced.

# wave

# wave -noreg -notation unsigned -bin -height 15 "/DPLL_MATLAB/\DPLL_MATLAB/HDL Black-Box\/VCO"

# 1 signal(s) traced.

# wave -noreg -notation unsigned -bin -height 15 "/DPLL_MATLAB/\DPLL_MATLAB/HDL Black-Box\/RF"

# 1 signal(s) traced.

# wave -noreg -notation unsigned -bin -height 15 "/DPLL_MATLAB/\DPLL_MATLAB/HDL Black-Box\/RESET"

# 1 signal(s) traced.

# wave -noreg -notation unsigned -bin -height 15 "/DPLL_MATLAB/\DPLL_MATLAB/HDL Black-Box\/PLL_LOCK"

# 1 signal(s) traced.

# wave -noreg -notation unsigned -bin -height 15 "/DPLL_MATLAB/\DPLL_MATLAB/HDL Black-Box\/DOWN"

# 1 signal(s) traced.

# wave -noreg -notation unsigned -bin -height 15 "/DPLL_MATLAB/\DPLL_MATLAB/HDL Black-Box\/UP"

# 1 signal(s) traced.

# run -all

#

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.