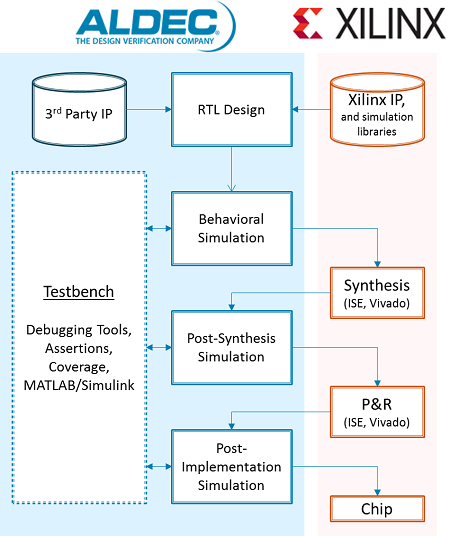

ザイリンクス (Xilinx) のデザインフロー

はじめに

現在、ザイリンクスにはFPGA/SoCの開発プラットフォームが2種類あります。Xilinx ISE Design SuiteはZynq-7000を含めザイリンクスの全プログラマブル・デバイスをサポートしています。Xilinx Vivado Design SuiteはSoCデザイン向けの次世代の開発プラットフォームで、よりシステムレベル統合とインプリメントに力を入れた設計となっています。アルデックでは、デバイスのサポート、ライブラリのサポート、GUIの統合について、この両方のプラットフォームに対応しています。アルデックはザイリンクスと連携して、アルデックのフローでザイリンクスの最新デバイスとテクノロジをすべてカバーできるようにしています。

デバイスファミリのサポート

アルデックのツールはザイリンクスのFPGA/SoCデバイスを、Virtex, Spartan, Artix, Kintex, Zynq-7000ファミリを含め、すべてサポートしています。CPLDについても、CoolRunnerやXC9500, XC4000ファミリなどすべてサポートしています。

ライブラリのサポート

ユーザーはザイリンクスのライブラリ・コンパイルユーティリティで自分のシミュレーションライブラリをコンパイルできます。ザイリンクスのライブラリ・コンパイルユーティリティはActive-HDLもRiviera-PROもサポートしています。

アルデックはザイリンクス向けにコンパイル済みのVHDL/Verilog/EDKライブラリも用意しており、いつでもアルデックのウェブサイトからダウンロードできます。

GUIの統合

ザイリンクスの公式ドキュメントでは、今のところザイリンクスの環境から直接起動できるのはISIMとModelSimだけとされています。ただし、回避方法を使えば、ザイリンクスのGUIからActive-HDLやRiviera-PROも起動できるようになります。

IPコアのシミュレーション

ザイリンクスから提供されているIPコアはすべてアルデックのツールでもサポートされています。ザイリンクスはVivado 2013.1以降、すべてのIPにP1735暗号化規格を導入しています。ザイリンクス環境のIPコアはすべてこの規格で暗号化されますが、アルデックはこれもサポートしています。こうしたIPもアルデックのツール上でシミュレーションできます。

レガシーデザインのインポート

アルデックはザイリンクスのFoundation SeriesやViewLogic/ViewDrawシリーズのスケマティックベースのレガシーデザインをインポートするユーティリティを用意しています。レガシープロジェクトのスケマティックファイルは、すべてのシンボルを含め、グラフィックごとアルデックのツールにインポートできます。インポートしたスケマティックファイルはブロックダイアグラム・エディタで編集して、そこからHDLコードを生成することも可能です。

ザイリンクスのライブラリでシミュレーション

Aldec向けに暗号化されたXilinx IP

Aldecをデフォルトシミュレータとして使用する

プロセッサベースのシステムのシミュレーション

DSPの協調シミュレーション (MATLAB/Simulink)

アルデックの関連する製品

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.